1010101010101010101010101010101010101

# CX25800 PCI Video Decoder with Mono Audio Input

**Data Sheet**

#### **Ordering Information**

| Model Number | Description | Package      | Operating<br>Temperature | Minimum<br>Order<br>Quantities |

|--------------|-------------|--------------|--------------------------|--------------------------------|

| CX25800      |             | 176-pin LQFP | 0 to +70 °C              |                                |

#### **Revision History**

| Revision | Date         | Description     |  |

|----------|--------------|-----------------|--|

| А        | July 2, 2007 | Initial Release |  |

© 2007, Conexant Systems, Inc. All Rights Reserved.

Information in this document is provided in connection with Conexant Systems, Inc. ("Conexant") products. These materials are provided by Conexant as a service to its customers and may be used for informational purposes only. Conexant assumes no responsibility for errors or omissions in these materials. Conexant may make changes to this document at any time, without notice. Conexant advises all customers to ensure that they have the latest version of this document and to verify, before placing orders, that information being relied on is current and complete. Conexant makes no commitment to update the information and shall have no responsibility whatsoever for conflicts or incompatibilities arising from future changes to its specifications and product descriptions.

No license, express or implied, by estoppel or otherwise, to any intellectual property rights is granted by this document. Except as provided in Conexant's Terms and Conditions of Sale for such products, Conexant assumes no liability whatsoever.

THESE MATERIALS ARE PROVIDED "AS IS" WITHOUT WARRANTY OF ANY KIND, EITHER EXPRESS OR IMPLIED, RELATING TO SALE AND/OR USE OF CONEXANT PRODUCTS INCLUDING LIABILITY OR WARRANTIES RELATING TO FITNESS FOR A PARTICULAR PURPOSE, CONSEQUENTIAL OR INCIDENTAL DAMAGES, MERCHANTABILITY, OR INFRINGEMENT OF ANY PATENT, COPYRIGHT OR OTHER INTELLECTUAL PROPERTY RIGHT. CONEXANT FURTHER DOES NOT WARRANT THE ACCURACY OR COMPLETENESS OF THE INFORMATION, TEXT, GRAPHICS OR OTHER ITEMS CONTAINED WITHIN THESE MATERIALS. CONEXANT SHALL NOT BE LIABLE FOR ANY SPECIAL, INDIRECT, INCIDENTAL, OR CONSEQUENTIAL DAMAGES, INCLUDING WITHOUT LIMITATION, LOST REVENUES OR LOST PROFITS, WHICH MAY RESULT FROM THE USE OF THESE MATERIALS.

Conexant products are not intended for use in medical, lifesaving or life sustaining applications. Conexant customers using or selling Conexant products for use in such applications do so at their own risk and agree to fully indemnify Conexant for any damages resulting from such improper use or sale.

The following are trademarks of Conexant Systems, Inc.: Conexant<sup>®</sup> and the Conexant C symbol. Product names or services listed in this publication are for identification purposes only, and may be trademarks of third parties. Third-party brands and names are the property of their respective owners.

For additional disclaimer information, please consult Conexant's Legal Information posted at <a href="https://www.conexant.com">www.conexant.com</a> which is incorporated by reference.

Reader Response: Conexant strives to produce quality documentation and welcomes your feedback. Please send comments and suggestions to tech.pubs@conexant.com. For technical questions, contact your local Conexant sales office or field applications engineer.

#### **Preliminary Information**

This document contains information on a new product. The parametric information, although not fully characterized, is the result of testing initial devices.

# CONEXANT

#### CX25800

### PCI Video Decoder with Mono Audio Input

The CX25800 is a highly flexible single chip solution that enables video and audio capture over a PCI bus. Designed for surveillance applications, the CX25800 accepts analog NTSC and PAL video from cameras, as well as line-level mono audio inputs from microphones. The CX25800 enables audio/video capture and playback on PC-based Digital Video Recorders (DVRs). The CX25800 also supports a variety of peripheral connectivity options via its GPIO pins, BT.656, I<sup>2</sup>S, MPEG port, and host port interfaces.

#### **Functional Block Diagram**

#### **Distinguishing Features**

#### Video Subsystem

- ◆ 10-bit video ADCs

- NTSC and PAL Composite video formats

- Capture resolution up to 720x576 (Square Pixel PAL)

- NTSC and PAL adaptive comb filter for 2-D Y/C luminance and chrominance separation

- ◆ AGC video circuit

- Multiple YCrCb and RGB pixel formats and YUV planar formats support on output

- Selectable pixel density: 16 and 24 bits per pixel

- Complex clipping of video source and VGA video overlay

- Allowance for different program control and color space/scaling for even and odd fields

- Support of Windows "Scatter/ Gather" DMA

- High-quality multitap horizontal and vertical image scaler for decoded video or 4:2:2 sources

- ITU-R BT.656 8-bit or 10-bit 4:2:2 output port

- ITU-R BT.656/VIP 2.0 pixel input port

- Flexible VBI data capture for closed captioning, teletext, and other analog data types

- Hue, brightness, contrast, saturation control for video decoder

(Continued on the next page)

#### Distinguishing Features (continued)

#### Audio Subsystem

- 10-bit A/D for mono analog audio input

- Decoded 48 kHz audio stream to PCI bus for real time encoding to MP3

- Integrated 90 dB SNR stereo audio DACs to drive sound card or headphones

- I<sup>2</sup>S input port for external source connectivity to on-board stereo DACs

- I<sup>2</sup>S output port to drive coaxial/ optical digital audio interface

- Flexible audio sample rate converter

#### Multipurpose I/O Subsystem

- Bidirectional 33 MBps VIP 2.0 Host port

- Bidirectional 10 MBps Intel/ Motorola-compatible General Purpose Host port

- Unidirectional 10 MBps parallel/ serial MPEG Transport/Data Stream port- compatible with all Conexant digital television channel demodulator ICs.

- MPEG Packet Synchronization

- User-defined General Purpose Input/Output pins

#### PCI Subsystem

- 5 independent functions each with Target/Master and Local register space (Video, Audio, MPEG Port, VIP 2.0 Host Port, GP Host Port)

- All RISC/Control programs executed on-chip

- On-chip SRAM for PCI data buffering Up/Down

- Vital product data

- DMA byte alignment

- ◆ PCI revision 2.3-compliant

#### Miscellaneous

- ACPI and power-down support

- Only one crystal for all video and audio decoding required

- 400 kHz serial bus master

- JTAG boundary scan interface

- Compact 176-pin LQFP

#### **Applications**

Surveillance camera systems

# **Contents**

| Figu | res        |                                                       | 11 |

|------|------------|-------------------------------------------------------|----|

| Tabl | es         |                                                       | 13 |

| 1    | Pro        | oduct Overview                                        | 15 |

|      | 1.1<br>1.2 | Functional Overview                                   |    |

|      |            | 1.2.1 Analog Video Capture                            | 16 |

|      |            | 1.2.1.1 Overview                                      | 16 |

|      |            | 1.2.1.2 Input Interface                               | 16 |

|      |            | 1.2.1.3 Image Scaler                                  |    |

|      |            | 1.2.1.4 Reduced Instruction Set Computer Engine       |    |

|      |            | 1.2.1.5 UltraLock™                                    |    |

|      |            | 1.2.1.6 Vertical Blanking Interval (VBI) Data Capture |    |

|      |            | 1.2.2 Analog Audio Capture                            |    |

|      |            | 1.2.3 ITU-R 656 4:2:2 Data Output                     |    |

|      |            | 1.2.4 ITU-R 656/VIP 2.0 Pixel Data Input              |    |

|      |            | 1.2.5 MPEG Data Port                                  |    |

|      |            | 1.2.6 General Purpose Host Interface Port             |    |

|      |            | 1.2.7 GPIO Port                                       |    |

|      |            | 1.2.8 Serial Bus Interface                            |    |

|      | 4.0        | 1.2.9 PCI Bus Interface                               |    |

|      | 1.3        | Pin Descriptions                                      |    |

| 2    | Fur        | nctional Description                                  | 27 |

|      | 2.1        | Audio Input                                           | 27 |

|      |            | 2.1.1 Overview                                        | 27 |

|      |            | 2.1.2 Analog Input ADC                                | 28 |

|      |            | 2.1.3 Audio PLL Initialization                        | 28 |

|      |            | 2.1.4 Input Source Select                             | 29 |

|      |            | 2.1.5 Audio Control and Sample Rate Converter         |    |

|      |            | 2.1.5.1 Audio Demodulator Sample Rate Converter       | 29 |

|      |            | 2.1.5.2 Volume                                        | 29 |

|      |            | 2.1.5.3 Balance                                       |    |

|      |            | 2.1.6 I <sup>2</sup> S Input and Output               |    |

|      |            | 2.1.6.1 I <sup>2</sup> S Input                        |    |

|      |            | 2.1.6.2 I <sup>2</sup> S Output                       | 32 |

|     | 2.1.7 | I <sup>2</sup> S Control                                     | . 32 |

|-----|-------|--------------------------------------------------------------|------|

|     |       | 2.1.7.1 Normal Mode                                          | . 33 |

|     |       | 2.1.7.2 OSR DAC Mode                                         | . 33 |

|     |       | 2.1.7.3 OSR ADC Mode                                         | . 34 |

|     |       | 2.1.7.4 Passthrough Mode                                     | . 35 |

|     |       | 2.1.7.5 Full Functionality Mode                              | . 36 |

|     | 2.1.8 | Audio DACs                                                   | . 37 |

| 2.2 | Gene  | ral Purpose Host Port                                        | . 38 |

|     | 2.2.1 | Introduction                                                 | . 38 |

|     | 2.2.2 | Host Port Overview                                           | . 38 |

|     | 2.2.3 | General Purpose Host Port Memory Space                       | . 46 |

|     | 2.2.4 | General Purpose Host Port Interface Register Access          | . 46 |

|     | 2.2.5 | General Purpose Host Interface External DMA Transfers        | . 46 |

|     | 2.2.6 | General Purpose Host Interface Signaling—Nonmultiplexed Mode | . 47 |

|     | 2.2.7 | General Purpose Host Interface Signaling—Multiplexed Mode    | . 49 |

| 2.3 | GPIO  |                                                              | . 51 |

|     | 2.3.1 | GPIO Pin Architecture                                        |      |

|     | 2.3.2 | GPIO Modes in CX25800                                        |      |

|     | 2.3.3 | GPIO Normal Mode                                             | . 55 |

|     | 2.3.4 | MPEG Parallel Port                                           |      |

|     | 2.3.5 | 8-Bit Parallel VIP Host Master                               |      |

|     | 2.3.6 | 4-Bit Parallel VIP Host Master                               |      |

|     | 2.3.7 | Video Synchronous Pixel (SPI) Mode                           |      |

|     | 2.3.8 | 10-Bit ITU-R. BT656 Output Mode                              |      |

|     | 2.3.9 | 8-Bit ITU-R. BT656/VIP 2.0 Pixel Input Mode                  |      |

|     |       | Host Port Chip Select Enable Mode                            |      |

| 2.4 |       | neral Component Interface                                    |      |

|     | 2.4.1 | PCI Functions                                                |      |

|     | 2.4.2 | PCI Configuration Space                                      |      |

|     | 2.4.3 | PCI Subsystem IDs                                            |      |

|     | 2.4.4 | Accessing VPD on the CX25800                                 |      |

|     | 2.4.5 | PCI Specification Regarding VPD Implementation               |      |

|     | 2.4.6 | Using VPD Data with Multiple Functions on One Card           |      |

|     | 2.4.7 | PCI Power Management                                         |      |

|     | 2.4.8 | Memory Space                                                 |      |

|     | 2.4.9 | PCI Data Streaming                                           |      |

|     |       | SRAM                                                         |      |

|     |       | FIFO Size Calculation                                        |      |

|     |       | Programmable FIFO                                            |      |

|     |       | RISC Instruction Queue                                       |      |

|     |       | Channel Management Data Structure                            |      |

|     |       | RISC Controller                                              |      |

|     |       | RISC Instructions                                            |      |

|     |       | Data Stream Control                                          |      |

|     |       | Data Stream User Guide                                       |      |

| 0.5 |       | PCI Master                                                   |      |

| 2.5 | MPH(  | A Data Port                                                  | 84   |

|     | 2.5.1  | Video C  | Compressors/Codecs                             | 84  |

|-----|--------|----------|------------------------------------------------|-----|

|     | 2.5.2  | Serial v | vs. Parallel Interface                         | 85  |

|     | 2.5.3  | MPEG     | ES (Elementary Stream)                         | 85  |

| 2.6 | Video  | Decode   | r                                              | 87  |

|     | 2.6.1  | Video I  | nput Multiplexer                               | 87  |

|     | 2.6.2  | 10-bit √ | /ideo Analog-to-Digital Converter              | 87  |

|     | 2.6.3  | Video S  | Signal Locking                                 | 87  |

|     |        | 2.6.3.1  | UltraLock Overview                             | 88  |

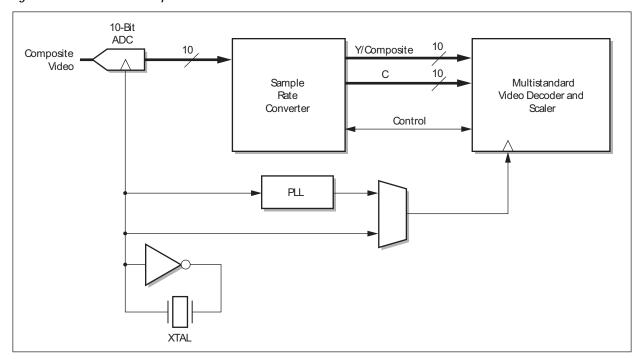

|     | 2.6.4  | Video S  | Sample Rate Converter                          | 89  |

|     |        | 2.6.4.1  | Flexible Video Timing Formats                  | 89  |

|     | 2.6.5  | Compo    | site Video Input Formats                       | 91  |

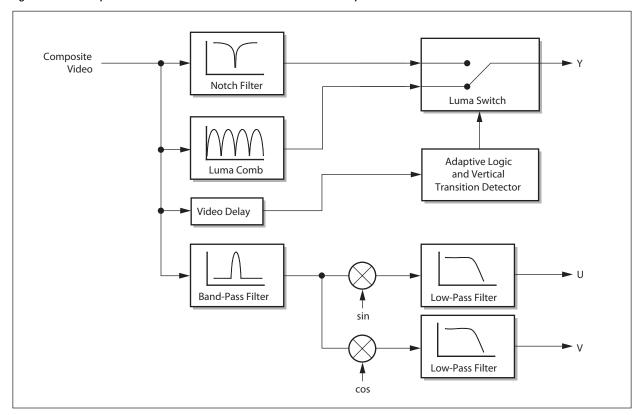

|     | 2.6.6  | Y/C Se   | paration and Chroma Demodulation               | 92  |

|     |        | 2.6.6.1  | The Y/C Separation Problem                     | 92  |

|     |        | 2.6.6.2  | Conexant Adaptive Comb Filter                  | 92  |

|     | 2.6.7  | Y/C Se   | paration and Chroma Demodulation               | 94  |

|     | 2.6.8  | Video S  | Scaling, Cropping, and Temporal Decimation     | 101 |

|     |        | 2.6.8.1  | Down-Scaling                                   | 101 |

|     |        | 2.6.8.2  | Vertical Scaling                               | 106 |

|     |        | 2.6.8.3  | Chrominance Scaling                            | 106 |

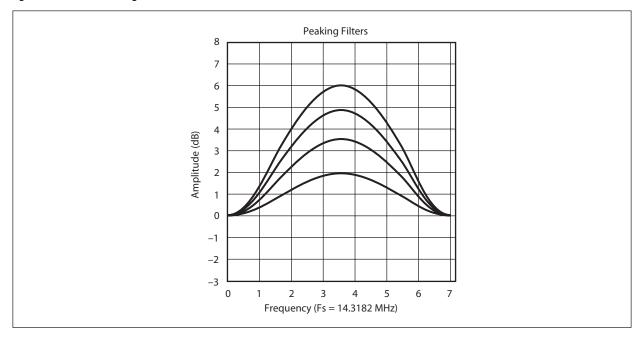

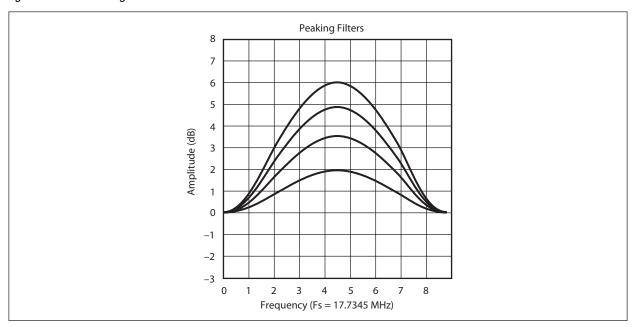

|     |        | 2.6.8.4  | Video Peaking Filters                          | 107 |

|     |        | 2.6.8.5  | The Horizontal Scaling Ratio (HSCALE) Register | 108 |

|     |        | 2.6.8.6  | The Vertical Scaling Ratio Register (VSCALE)   | 109 |

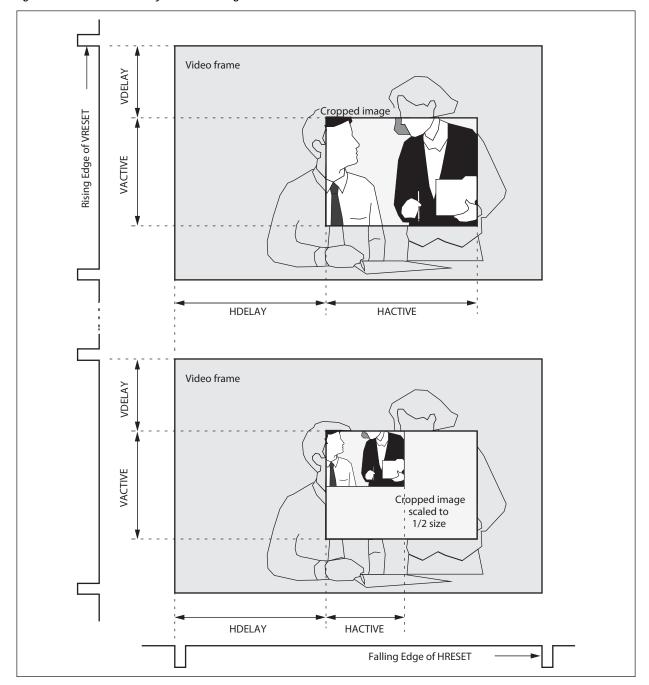

|     | 2.6.9  | Image (  | Cropping                                       | 111 |

|     | 2.6.10 | Croppir  | ng Registers                                   | 112 |

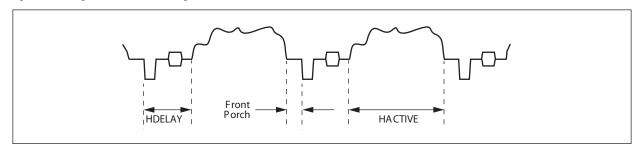

|     |        | 2.6.10.1 | Horizontal Delay Register (HDELAY)             | 112 |

|     |        |          | 2 Horizontal Active Register (HACTIVE)         |     |

|     |        |          | 3 The Vertical Delay Register (VDELAY)         |     |

|     |        |          | The Vertical Active Register (VACTIVE)         |     |

|     |        |          | ral Decimation                                 |     |

|     | 2.6.12 |          | Adjustments                                    |     |

|     |        |          | The Hue Adjust Register                        |     |

|     |        |          | 2 The Contrast Adjust Register                 |     |

|     |        |          | 3 The Saturation Adjust Registers              |     |

|     |        |          | The Brightness Register                        |     |

|     |        |          | 5 Automatic Chrominance Gain Control (ACGC)    |     |

|     |        |          | olor Detection and Removal                     |     |

|     |        |          |                                                |     |

|     |        |          | ta Output Interface                            |     |

|     |        |          | ne Output Mode                                 |     |

|     |        |          | 556 Output Interface                           |     |

| 0.7 |        |          | 656/VIP 2.0 8-bit Pixel Input Interface        |     |

| 2.7 |        |          | Master                                         |     |

|     | 2.7.1  |          | Ction                                          |     |

|     | 2.7.2  |          | Host Master Overview                           |     |

|     | 2.7.3  |          | Host Master System Functionality               |     |

|     |        | 2.7.3.1  | Downstream DMA Channel                         |     |

|     |        | 2.7.3.2  | Upstream DMA Channel                           | 128 |

|   |      |         | 2.7.3.3 VIP External Register Access         | 129 |

|---|------|---------|----------------------------------------------|-----|

|   |      |         | 2.7.3.4 VIP Local Register Access            | 129 |

|   |      | 2.7.4   | VIP Memory Space                             | 130 |

|   |      | 2.7.5   | VIP Address Space                            | 130 |

| 3 | Fle  | etrica  | Il Interfaces                                | 131 |

| 3 |      |         |                                              |     |

|   | 3.1  |         | Interfaces                                   |     |

|   |      | 3.1.1   | Analog Signal Selection                      |     |

|   |      | 3.1.2   | Multiplexer Considerations                   |     |

|   |      |         | 3.1.2.1 ADCs                                 |     |

|   |      | 3.1.3   | Power-Up Operation                           |     |

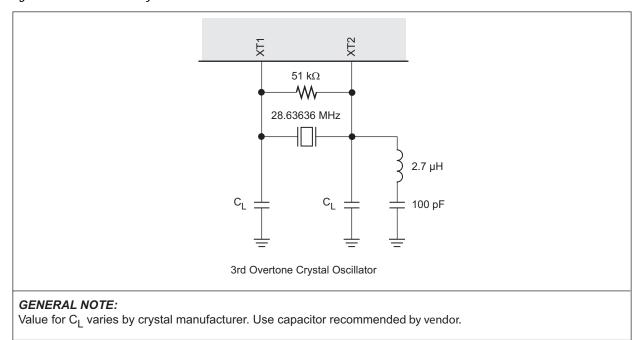

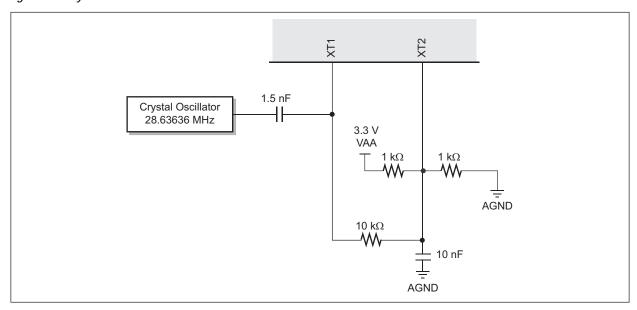

|   |      | 3.1.4   | Crystal Inputs and Clock Generation          |     |

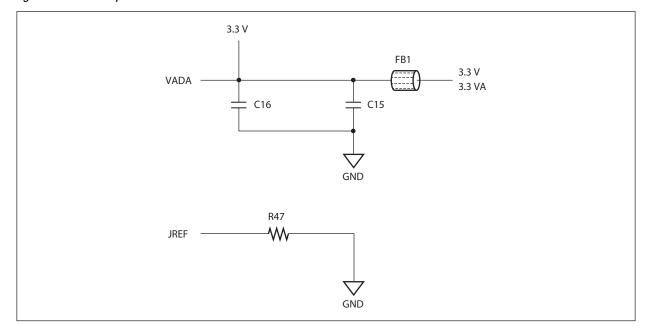

|   |      | 3.1.5   | Audio Considerations                         |     |

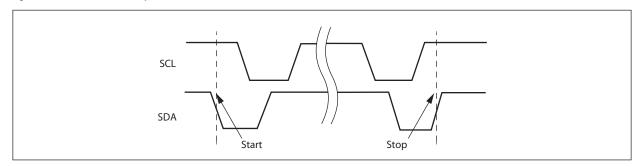

|   | 3.2  | Seria   | al Bus Interface                             |     |

|   |      | 3.2.1   | Serial Bus Serial EEPROM Interface           |     |

|   |      | 3.2.2   | EEPROM Upload at PCI Reset                   | 138 |

|   |      | 3.2.3   | Register Load from BIOS                      |     |

|   | 3.3  | Vital I | Product Data                                 |     |

|   |      | 3.3.1   | Required VPD                                 | 139 |

|   |      | 3.3.2   | VPD Access.                                  | 140 |

|   |      | 3.3.3   | VPD Address                                  | 140 |

|   |      | 3.3.4   | VPD Read                                     | 141 |

|   |      | 3.3.5   | VPD Write                                    | 142 |

|   | 3.4  | Powe    | er Management Interface                      | 143 |

|   |      | 3.4.1   | PME#                                         |     |

|   |      | 3.4.2   | D3 Power States                              | 143 |

|   | 3.5  | JTAG    | G Interface                                  | 144 |

|   |      | 3.5.1   | Need for Functional Verification             | 144 |

|   |      | 3.5.2   | JTAG Approach to Testability                 | 144 |

|   |      | 3.5.3   | Optional Device ID Register                  | 145 |

|   |      | 3.5.4   | Verification with the TAP Controller         | 145 |

| 4 | PC   | Boar    | d Layout Considerations                      | 147 |

|   |      |         |                                              |     |

|   | 4.1  |         | out Considerations                           |     |

|   |      | 4.1.1   | Capacitors                                   |     |

|   |      | 4.1.2   | Components                                   | 147 |

| 5 | Re   | gisters | S                                            | 149 |

|   | 5.1  | PCI (   | Configuration Registers: Function 0: Video   | 149 |

|   | 5.2  |         | Configuration Registers: Function 1: Audio   |     |

|   | 5.3  |         | Configuration Registers: Function 2: MPEG TS |     |

|   | 5.4  |         | Configuration Registers: Function 3: VIP     |     |

|   | 5.5  |         | Configuration Registers: Function 4: Host    |     |

|   | 5.6  | Memo    | ory Mapped Registers: Miscellaneous Control  | 196 |

|   | 5.7  | Memo    | ory Mapped Registers: Function 0: Video      | 207 |

|   | 5.8  |         | ory Mapped Registers: Function 1: Audio      |     |

|   | 5.9  |         | ory Mapped Registers: Function 2: MPEG TS    |     |

|   | 5.10 |         | ory Mapped Registers: Function 3: VIP        |     |

|   | 5.11 | Memo    | ory Mapped Registers: Function 4: Host       | 250 |

| • |     | ectrical and Mechanical ciffications |

|---|-----|--------------------------------------|

|   | 6.1 | DC Electrical Parameters             |

|   | 6.2 | AC Electrical Parameters             |

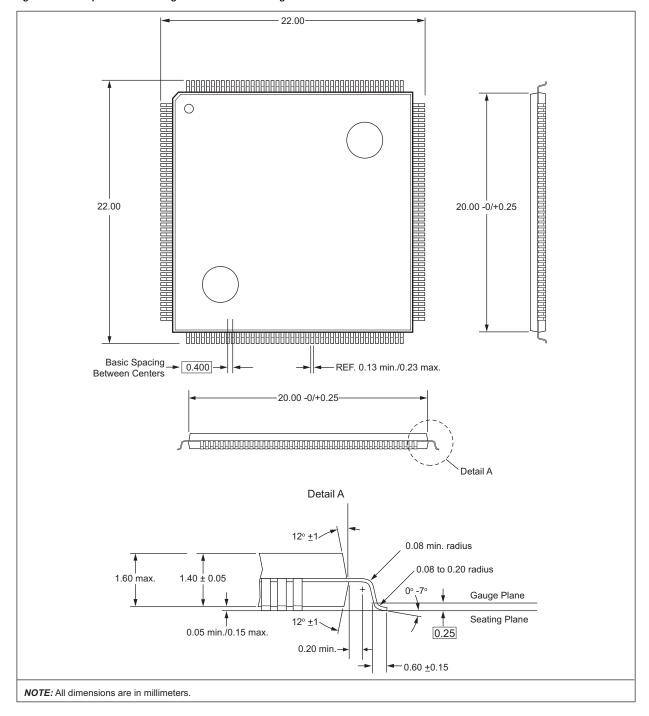

|   | 6.3 | Package Mechanical Drawing           |

# **Figures**

| Figure 1.  | CX25800 Detailed Block Diagram1                                                                          | 5          |

|------------|----------------------------------------------------------------------------------------------------------|------------|

| Figure 2.  | CX25800 Pinout Diagram                                                                                   | 2C         |

| Figure 3.  | Simplified Block Diagram of CX25800 Audio Subsystem                                                      | 35         |

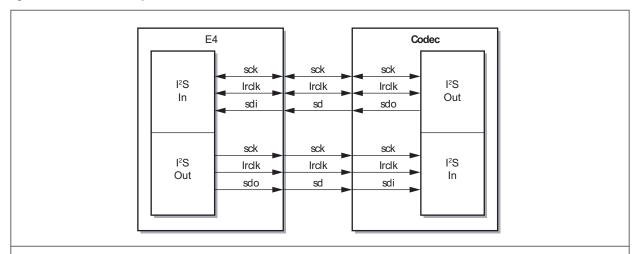

| Figure 4.  | Normal Mode Operation                                                                                    | 33         |

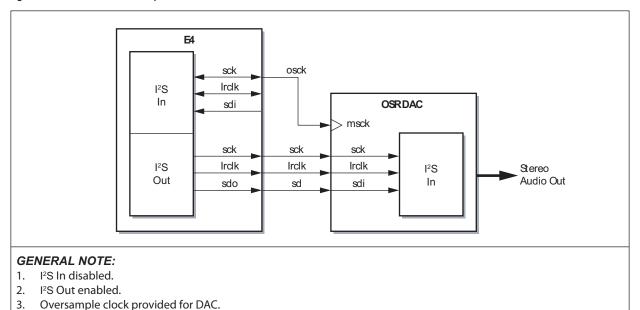

| Figure 5.  | OSR DAC Mode Operation                                                                                   | 34         |

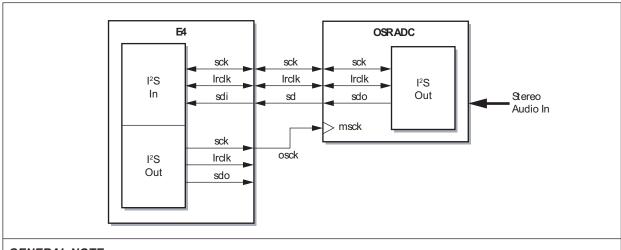

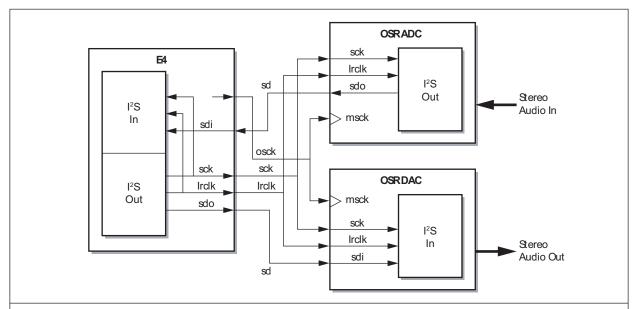

| Figure 6.  | OSR ADC Mode Operation                                                                                   | 34         |

| Figure 7.  | Passthrough Mode Operation                                                                               | 35         |

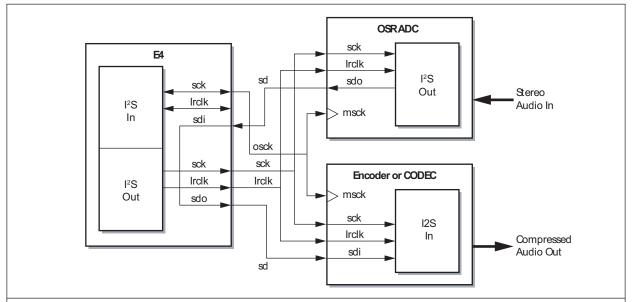

| Figure 8.  | Full Functionality Mode                                                                                  | 36         |

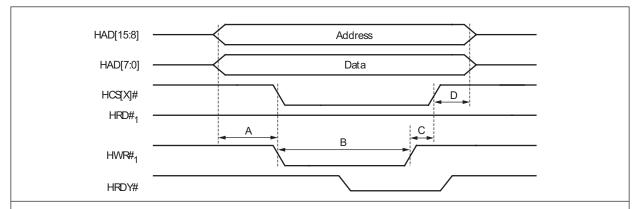

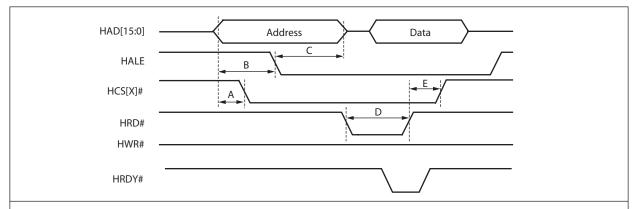

| Figure 9.  | Host Interface Write Operation—Intel Style (Accessing an External Device) 4                              | <b>1</b> 7 |

| Figure 10. | Host Interface Write Operation—Motorola Style (Accessing an External Device) 4                           | <b>F</b> 7 |

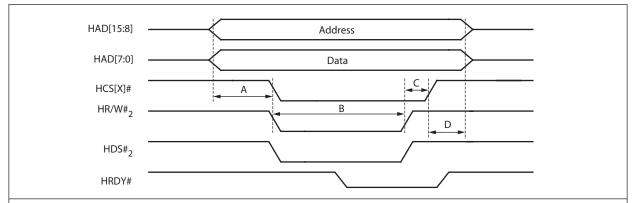

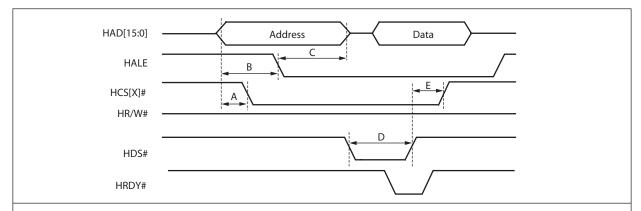

| Figure 11. | Host Interface Read Operation—Intel Style (Accessing an External Device) 4                               | 18         |

| Figure 12. | Host Interface Read Operation—Motorola Style (Accessing an External Device) 4                            | 18         |

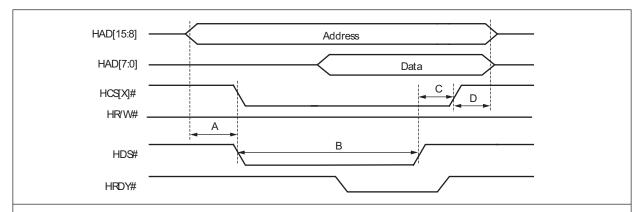

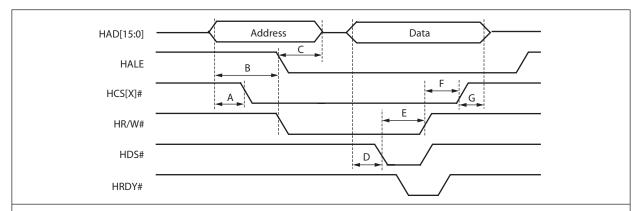

| Figure 13. | Host Interface Read Operation—Intel Style Multiplexed Address/Data Bus (Accessing ar External Device)    |            |

| Figure 14. | Host Interface Read Operation—Motorola Style Multiplexed Address/Data Bus (Accessin an External Device)  |            |

| Figure 15. | Host Interface Write Operation—Intel Style Multiplexed Address/Data Bus (Accessing an External Device)   | า          |

| Figure 16. | Host Interface Write Operation—Motorola Style Multiplexed Address/Data Bus (Accessin an External Device) |            |

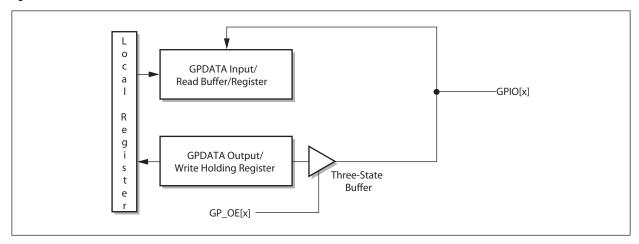

| Figure 17. | GPIO Pin Architecture                                                                                    | 51         |

| Figure 18. | MPEG Parallel Port5                                                                                      | 56         |

| Figure 19. | 8-bit Parallel VIP Host Master5                                                                          | 57         |

| Figure 20. | Video Synchronous Pixel (SPI) Mode                                                                       | 58         |

| Figure 21. | 10-bit ITU-R. BT656 Output Mode5                                                                         | 36         |

| Figure 22. | 8-bit ITU-R. BT656/VIP 2.0 Pixel Input Mode                                                              | 30         |

| Figure 23. | Host Port Chip Select Enable Mode6                                                                       | 51         |

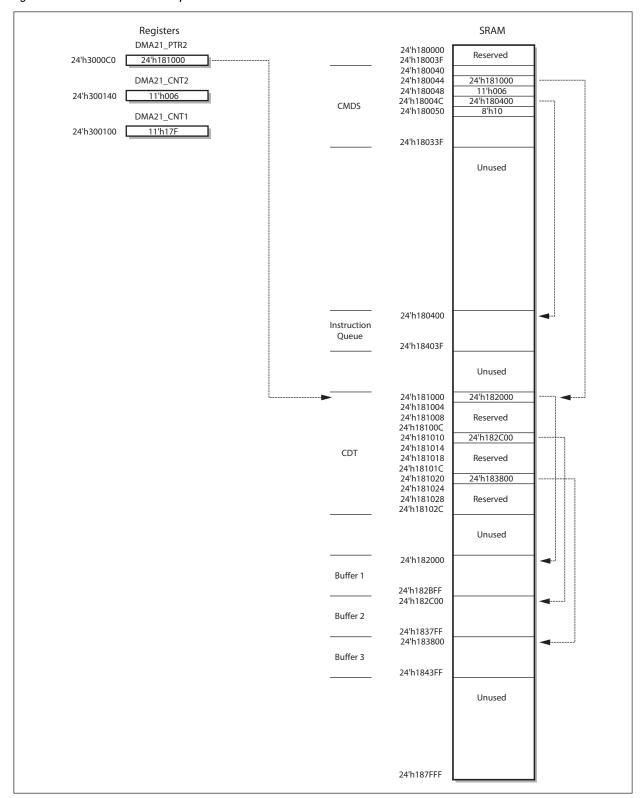

| Figure 24. | SRAM Resource Example7                                                                                   | 'C         |

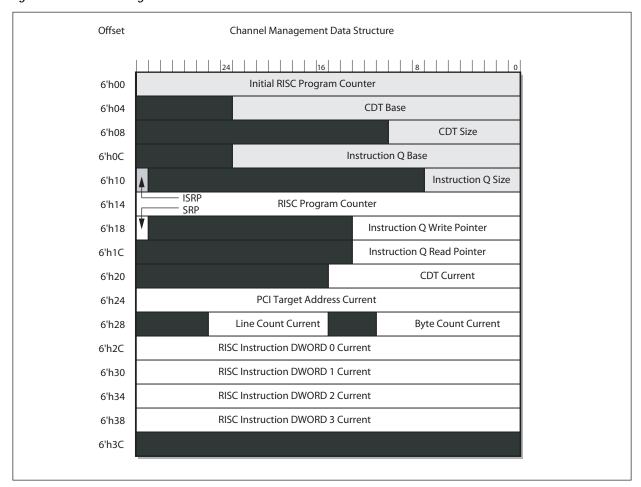

| Figure 25. | Channel Management Data Structure                                                                        | '2         |

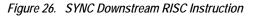

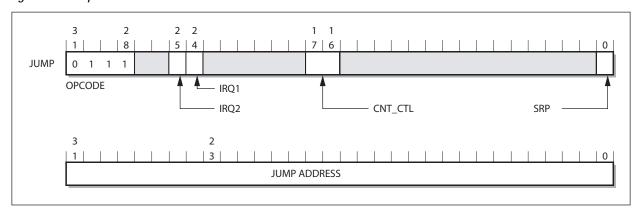

| Figure 26. | SYNC Downstream RISC Instruction                                                                         | 74         |

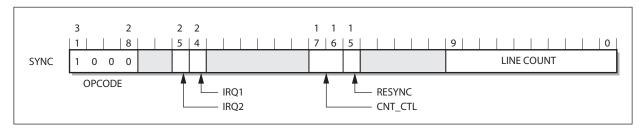

| Figure 27. | WRITE Downstream RISC Instruction                                                                        | 75         |

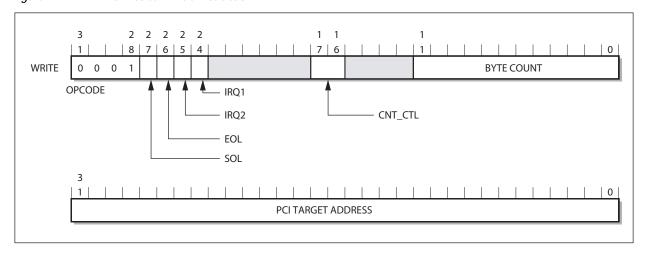

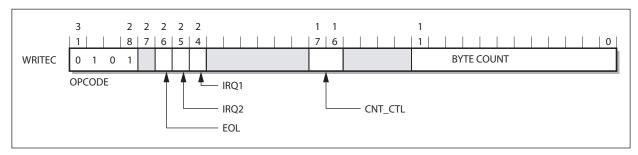

| Figure 28. | WRITEC Downstream RISC Instruction                                                                       | '5         |

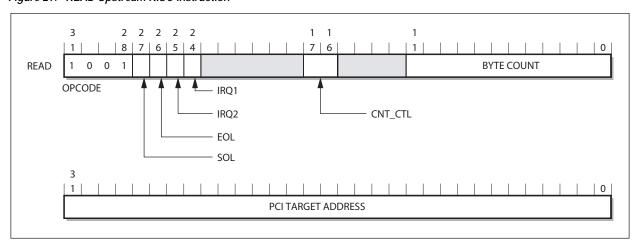

| Figure 29. | READ Upstream RISC Instruction                                                                           | '5         |

| Figure 30. | READC Upstream RISC Instruction                                                                          | '6         |

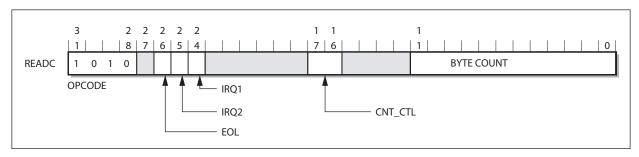

| Figure 31. | SKIP RISC Instruction                                                                                    | '6         |

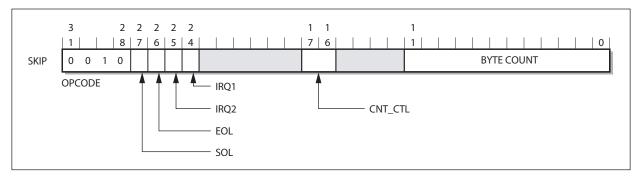

| Figure 32. | Jump RISC Instruction                                                                                    | '6         |

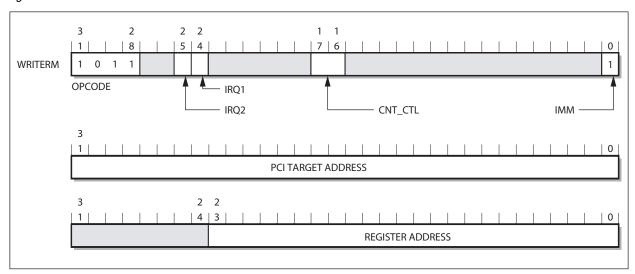

| Figure 33. | WRITERM RISC Instruction                                                                     | 77     |

|------------|----------------------------------------------------------------------------------------------|--------|

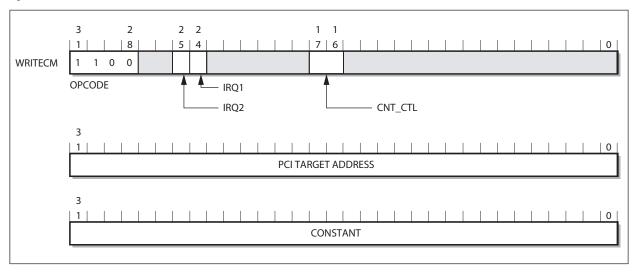

| Figure 34. | WRITECM RISC Instruction                                                                     | 77     |

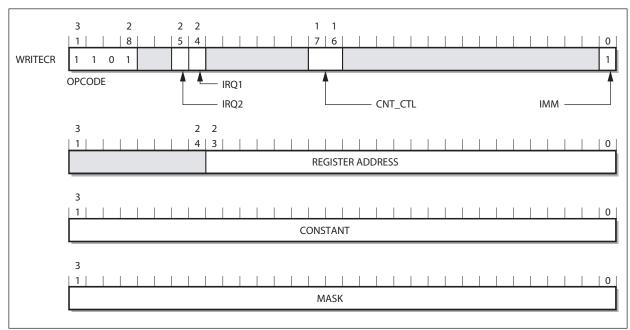

| Figure 35. | WRITECR RISC Instruction                                                                     | 78     |

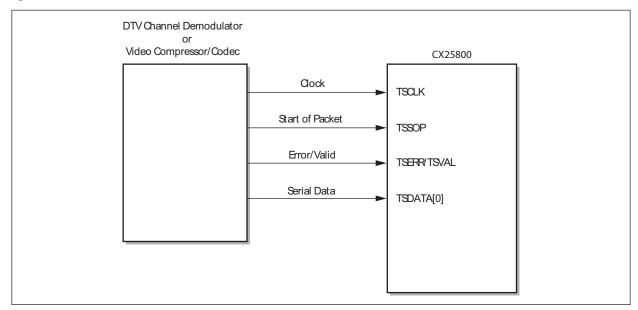

| Figure 36. | MPEG Port Serial Interface                                                                   | 85     |

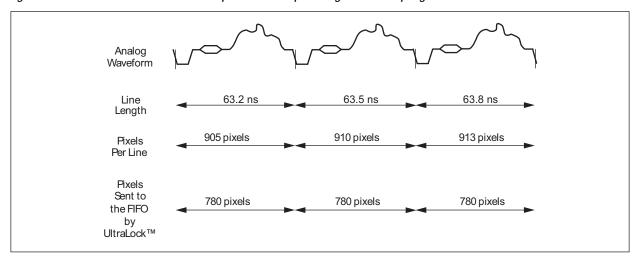

| Figure 37. | UltraLock Behavior for NTSC Square Pixel Output using 4x Fsc Sampling Rate .                 | 88     |

| Figure 38. | UltraLock and Sample Rate Converter                                                          | 89     |

| Figure 39. | Y/C Separation and Chroma Demodulation Circuit for Composite NTSC/PAL Video                  | 93     |

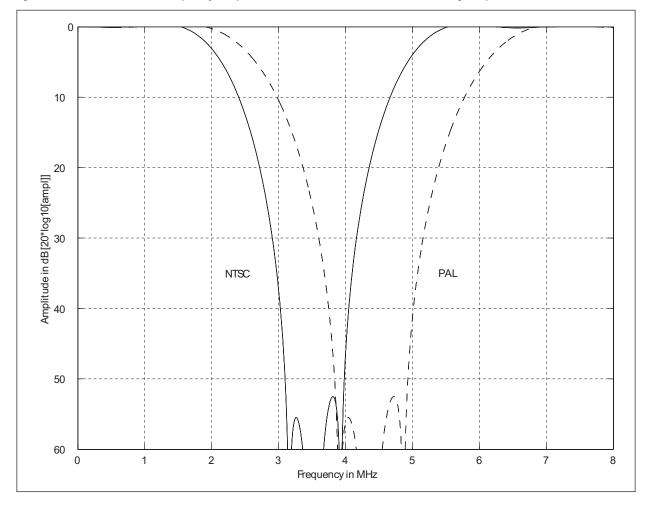

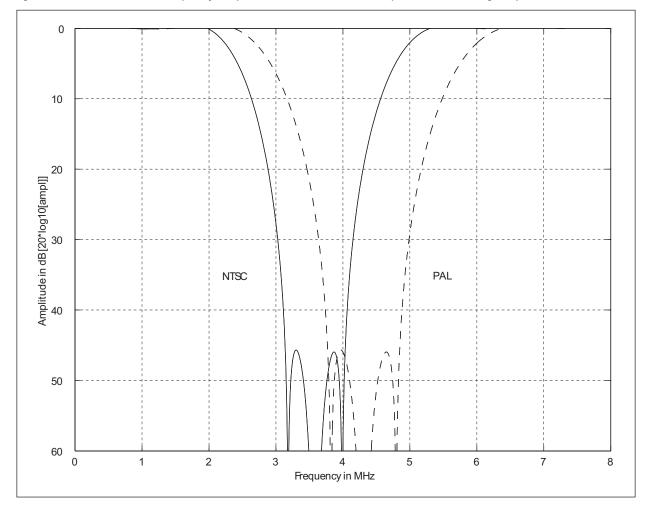

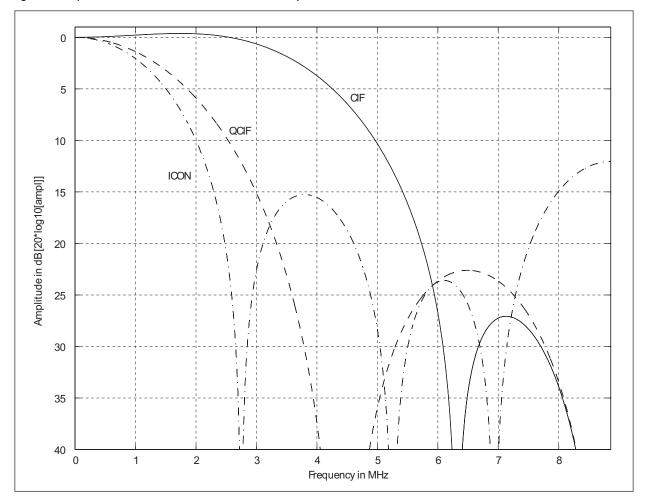

| Figure 40. | Luma Notch Filter Frequency Responses for NTSC and PAL @ 4x Fsc Decoding F cies              | 94     |

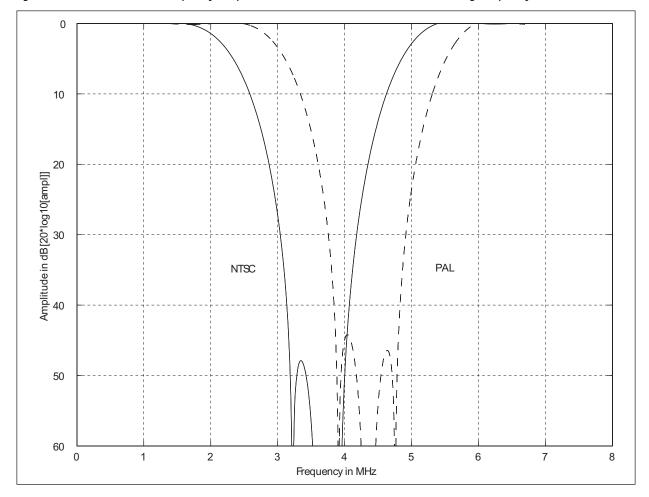

| Figure 41. | Luma Notch Filter Frequency Responses for NTSC and PAL @ Square Pixel Decod quencies         | 95     |

| Figure 42. | Luma Notch Filter Frequency Responses for NTSC and PAL @ 13.5-MHz Decodir quency             | 96     |

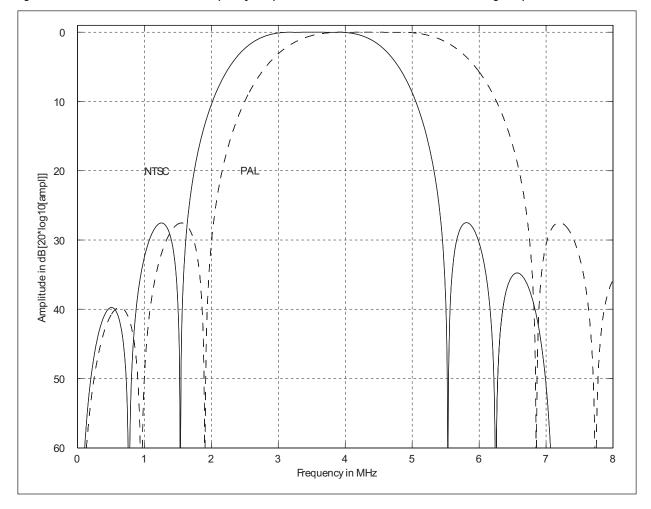

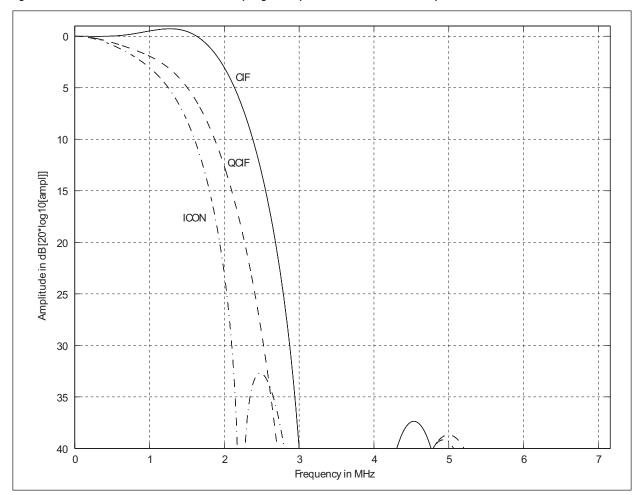

| Figure 43. | Chroma Band Pass Filter Frequency Responses for NTSC and PAL @ 4x Fsc Dec Frequencies        | 97     |

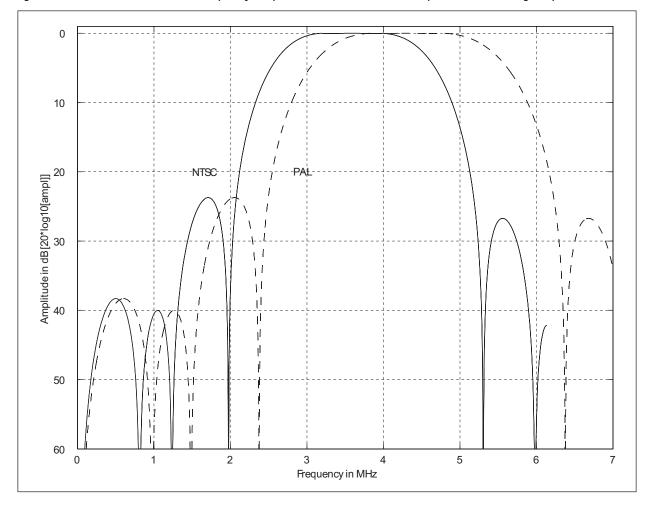

| Figure 44. | Chroma Band Pass Filter Frequency Responses for NTSC and PAL @ Square Pix coding Frequencies |        |

| Figure 45. | Chroma Band Pass Filter Frequency Responses for NTSC and PAL @ 13.5-MHz De Frequency         | _      |

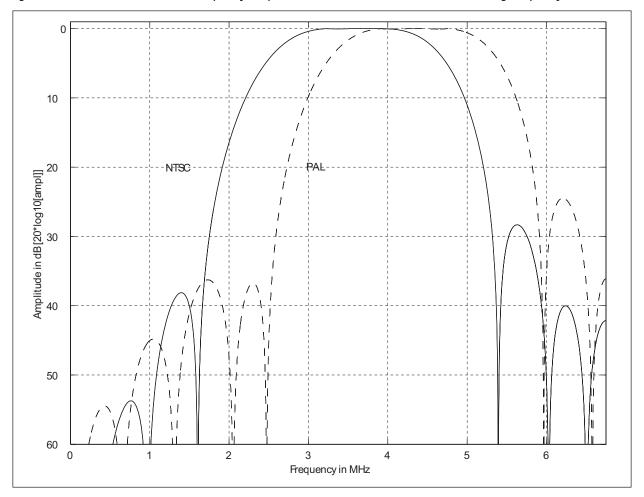

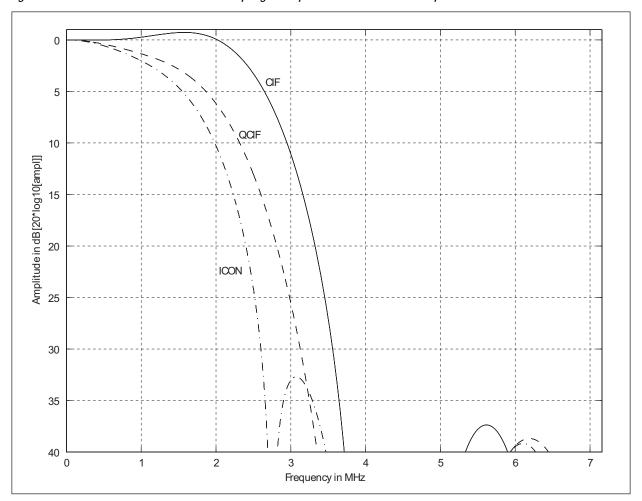

| Figure 46. | Optional Horizontal Luma Low-Pass Filter Responses for NTSC                                  | 102    |

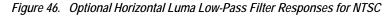

| Figure 47. | Optional Horizontal Luma Low-Pass Filter Responses for PAL                                   | 103    |

| Figure 48. | Combined Luma Notch 2x Oversampling and Optional Low-Pass Filter Response fo 104             | r NTSC |

| Figure 49. | Combined Luma Notch 2x Oversampling and Optional Low-Pass Filter Response SECA               |        |

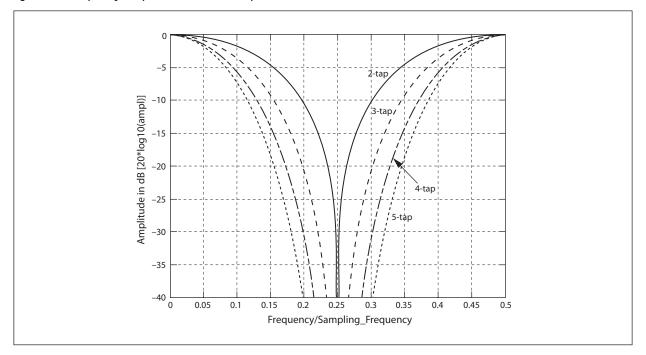

| Figure 50. | Frequency Responses for the Four Optional Vertical Luma Low-Pass Filters                     | 106    |

| Figure 51. | NTSC Peaking Filters                                                                         | 107    |

| Figure 52. | PAL Peaking Filters                                                                          | 107    |

| Figure 53. | Effect of the Delay and Active Registers                                                     | 111    |

| Figure 54. | Regions of the Video Signal                                                                  | 112    |

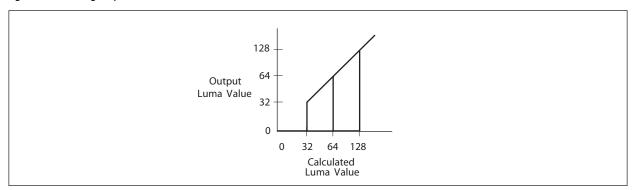

| Figure 55. | Coring Map                                                                                   |        |

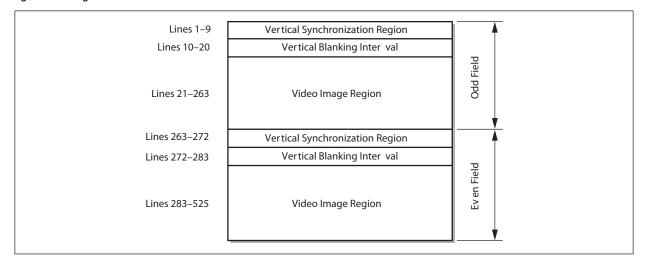

| Figure 56. | Regions of the NTSC Video Frame                                                              |        |

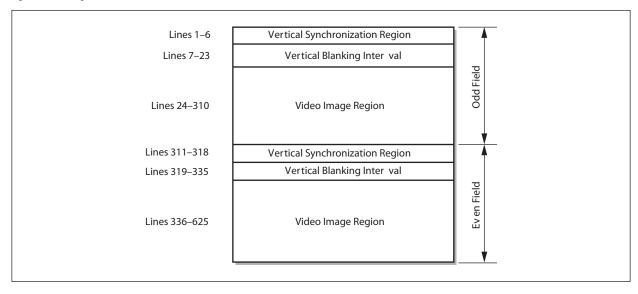

| Figure 57. | Regions of the PAL Video Frame (Fields 1, 2, 5, and 6)                                       |        |

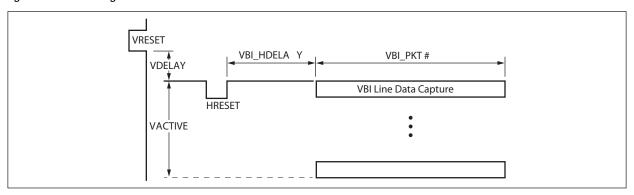

| Figure 58. | VBI Timing                                                                                   |        |

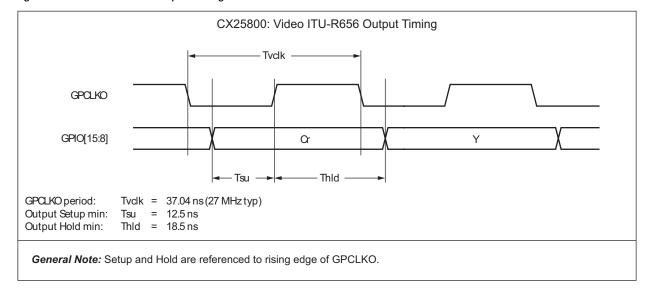

| Figure 59. | Video ITU-R 656 Output Timing                                                                |        |

| Figure 60. | MPEG 2 Decoder to CX25800 ITU-R656 Connection, Example 1                                     |        |

| Figure 61. | MPEG 2 Decoder to CX25800 ITU-R656 Connection, Example 2                                     |        |

| Figure 62. | Data Transfer from VIP 2.0 Slave to Host through CX25800                                     |        |

| Figure 63. | Data Transfer from Host to VIP Slave through CX25800                                         |        |

| Figure 64. | VIP External Register Access                                                                 |        |

| Figure 65. | Resistor-Divider Network                                                                     |        |

| Figure 66. | Fundamental Crystal Oscillator                                                               |        |

| Figure 67. | 3rd Overtone Crystal Oscillator                                                              |        |

| Figure 68. | Crystal Clock Oscillator                                                                     |        |

| Figure 69. | Audio Implementation                                                                         |        |

| Figure 70. | The Relationship Between SIC and SID                                                         |        |

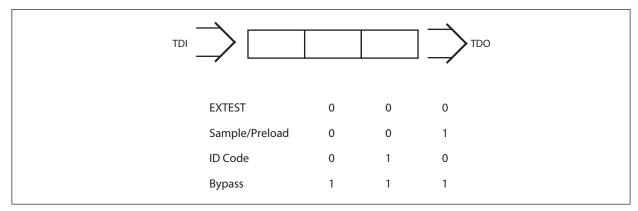

| Figure 71. | Instruction Register                                                                         |        |

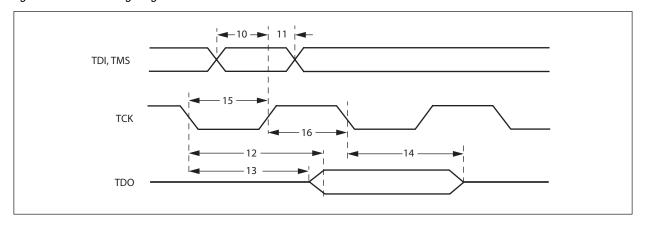

| Figure 72. | JTAG Timing Diagram                                                                          |        |

| Figure 73. | 176-pin TQFP Package Mechanical Drawing                                                      | 261    |

# **Tables**

| Table 1.  | Pin Descriptions Grouped by Pin Function                  | 21                 |

|-----------|-----------------------------------------------------------|--------------------|

| Table 2.  | CX25800 Applications Enabled by Host Port Peripherals     | 38                 |

| Table 3.  | GPHP Pin Definition                                       | 39                 |

| Table 4.  | GPHP Memory Space                                         | 46                 |

| Table 5.  | GPIO Pin Numbers                                          | 52                 |

| Table 6.  | GPIO Mode Allocation                                      | 53                 |

| Table 7.  | GPIO Mode versus Pin Usage                                | 53                 |

| Table 8.  | PCI Functions                                             | 62                 |

| Table 9.  | CX25800 Memory Space                                      | 65                 |

| Table 10. | MA Channel Assignment                                     | 66                 |

| Table 11. | Channel Management Data Structure                         | 71                 |

| Table 12. | SOL/EOL Combinations                                      | <b>7</b> 9         |

| Table 13. | WRITERM Registers                                         | 80                 |

| Table 14. | Video Decoding Formats                                    | 90                 |

| Table 15. | Sample Rate Conversion                                    | 90                 |

| Table 16. | Video Input Formats Supported by the CX25800              | 91                 |

| Table 17. | Register Values for Square Pixel Video Input Formats      | 91                 |

| Table 18. | Scaling Ratios for Popular Formats Using Frequency Values | 110                |

| Table 19. | 4x Fsc Pixel Values                                       |                    |

| Table 20. | VIP Host Master Interface Pin Description                 | 120                |

| Table 21. | Memory VIP Space                                          | 130                |

| Table 22. | EEPROM Read Sequence                                      | 138                |

| Table 23. | VPD Addresses                                             | 140                |

| Table 24. | VPD Read Sequence                                         | 141                |

| Table 25. | VPD Write Sequence                                        | 142                |

| Table 26. | Device Identification Register                            | 145                |

| Table 27. | Register Types                                            |                    |

| Table 28. | Recommended Operating Conditions                          | 257                |

| Table 29. | Absolute Maximum Ratings                                  |                    |

| Table 30. | DC Characteristics                                        | 259                |

| Table 31. | Clock Timing Parameters                                   | 260                |

| Table 32. | Power Supply Current Parameters                           | 2 <mark>6</mark> 0 |

| Table 33. | JTAG Timing Parameters                                    | 260                |

|           |                                                           |                    |

### **Product Overview**

### 1.1 Functional Overview

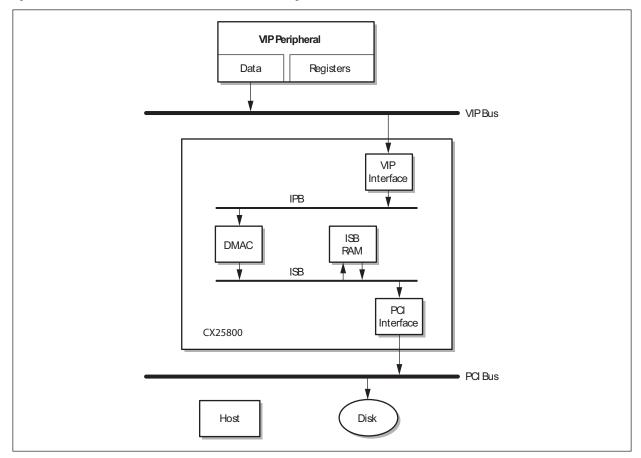

The CX25800 is implemented as a multifunction PCI bus master and fabricated in an advanced CMOS process operating from +3.3 V I/P and 1.8 V (digital core) power supplies. PCI inputs are +5 V and 3.3 V tolerant.

The CX25800 is designed to enable high-functionality broadcast- centric PC cards that require high speed Input/Output (I/O) capability. This capability is necessary to support simultaneous compressed and uncompressed digital video/audio data flows in conjunction with hardware MPEG II/MPEG IV encoders and decoders.

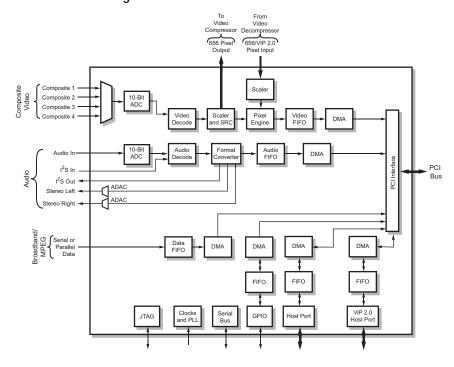

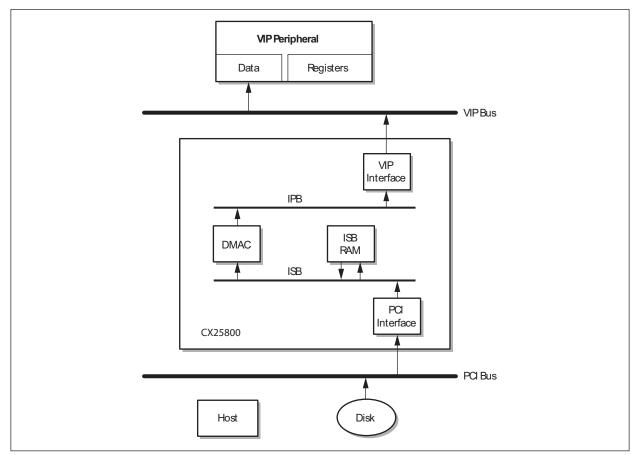

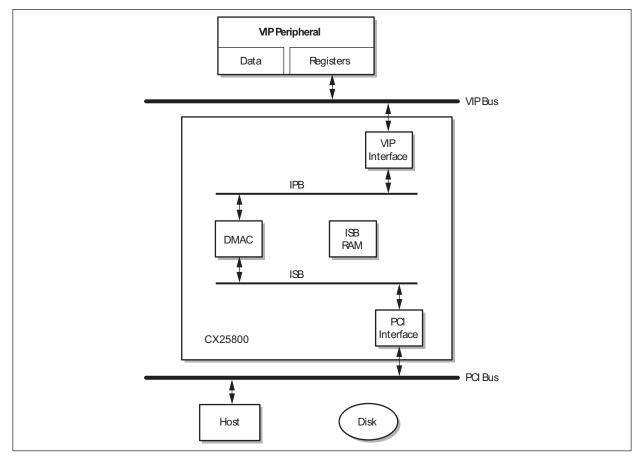

Figure 1 illustrates a block diagram of the CX25800.

Figure 1. CX25800 Detailed Block Diagram

Product Overview CX25800 Data Sheet

#### 1.2 Detailed Features

#### 1.2.1 Analog Video Capture

#### 1.2.1.1 Overview

The CX25800 integrates a 10-bit NTSC/PAL composite video decoder, image resizer/ scaler, Direct Memory Access (DMA) controller, and Peripheral Component Interface (PCI) Bus master on a single device. The CX25800 can place video data directly into host memory for video capture applications and into a target video display frame buffer for video overlay applications. As a PCI initiator, the CX25800 can take control of the PCI bus as soon as it is available, thereby avoiding the need for onboard frame buffers. The CX25800 contains a pixel data First In, First Out (FIFO) to decouple the high-speed PCI bus from the continuous video data stream. The video data input can be scaled, color-translated, and burst-transferred to a target location on a field basis.

#### 1.2.1.2 Input Interface

Analog video signals are input to the CX25800 through a four-input multiplexer. An Automatic Gain Control (AGC) circuit enables the CX25800 to compensate for nonstandard amplitudes in the analog signal input.

#### 1.2.1.3 Image Scaler

The CX25800 can reduce the video image size in both horizontal and vertical directions independently, using arbitrarily selected scaling ratios. The X and Y dimensions can be scaled down to one-sixteenth of the full resolution. Horizontal scaling is implemented with a six-tap interpolation filter, while up to five-tap interpolation is used for vertical scaling with a line store. The video image can be arbitrarily cropped by reducing the number of active scan lines and active horizontal pixels per line. The CX25800 supports a temporal decimation feature that reduces video bandwidth. This is accomplished by allowing frames or fields to be dropped from a video sequence at fixed but arbitrarily selected intervals.

CX25800 Data Sheet Product Overview

#### 1.2.1.4 Reduced Instruction Set Computer Engine

The CX25800 enables separate destinations for the odd and even video fields, each controlled by a pixel Reduced Instruction Set Computer (RISC) instruction list. This instruction list is created by the CX25800 device driver and can be run in the onboard memory or host memory. The instructions control the transfer of pixels to target memory locations on a byte resolution basis. Complex clipping can be accomplished by the instruction list, blocking the generation of PCI bus cycles for pixels that are not to be seen on the display.

The DMA channels can be programmed on a field basis to deliver the video data in packed or planar format. In packed mode, YCrCb data is stored in a single continuous block of memory. In planar mode, the YCrCb data is separated into three streams which are burst to different target memory blocks. Having the video data in planar format is useful for applications where the data compression is accomplished through software and the CPU.

#### 1.2.1.5 UltraLock™

The CX25800 employs a proprietary technique known as UltraLock to lock to the incoming analog video signal. It always generates the required number of pixels per line from an analog source in which line length can vary by as much as a few microseconds. UltraLock's digital locking circuitry enables the CX25800 to lock onto video signals quickly and accurately, regardless of their source. Because the technique is completely digital, UltraLock can recognize unstable signals caused by VCR head switches or any other deviation and adapt the locking mechanism to accommodate the source. UltraLock uses nonlinear techniques that are difficult, if not impossible, to implement in genlock systems. And, unlike linear techniques, it adapts the locking mechanism automatically.

#### 1.2.1.6 Vertical Blanking Interval (VBI) Data Capture

The CX25800 provides a flexible solution for capturing and decoding disparate VBI data types such as closed caption data, teletext, Vertical Internal Time and Control (VITC) codes, HTML data, or multicast data. The CX25800 can operate in a VBI Line Output mode, in which the VBI data is only captured during selected lines. This mode of operation enables concurrent capture of VBI lines containing ancillary data and normal video image data. In addition, the CX25800 supports a VBI Frame Output mode in which every line in the video frame is treated as if it were a VBI line. This mode of operation is designed for use with still-frame capture and processing applications where sophisticated image decoding can be performed in the software domain.

Product Overview CX25800 Data Sheet

#### 1.2.2 Analog Audio Capture

The CX25800 captures mono analog audio. The decoded audio is sample-rate converted to a 48-kHz Pulse Code Modulation (PCM) signal to simplify processing and interfacing. This 48-kHz stream can be routed to the built-in +85 dB Signal-to-Noise Ratio (SNR) stereo audio Digital-to-Analog Converters (DACs) for connection to the PC's sound card or headphones, to an external digital-audio interface, or to the PCI bus and host for direct capture by a software audio codec.

If capture of line-level stereo audio signals is required, an inexpensive audio Analog-to-Digital Converter (ADC) can be directly connected to the CX25800's I<sup>2</sup>S input port and controlled through the serial bus master.

### 1.2.3 ITU-R 656 4:2:2 Data Output

The CX25800 provides a 27-MHz, 8- or 10-bit ITU-R 656 decoded video output interface to allow connection of a third-party MPEG II encoder or other type of video codec. This is useful when the host CPU is not powerful enough to perform such tasks in software, or when high-quality encoding must be achieved.

### 1.2.4 ITU-R 656/VIP 2.0 Pixel Data Input

The CX25800 provides a 27-MHz, 8-bit ITU-R 656 decoded video input interface. This allows a third-party MPEG II decoder or codec to send 4:2:2 data over the PCI bus to a target video display frame buffer for video overlay.

#### 1.2.5 MPEG Data Port

Channel demodulators used for digital television or broadband data applications over terrestrial, satellite, or cable networks can be directly connected to the CX25800's MPEG data port. As a result, transport streams can be delivered to the host for subsequent storage to disk or software decode. Either parallel, common-interface Digital Video Broadcasting (DVB) or serial data paths from the channel demodulator can be supported at data transfer rates of up to 80 Mbps. If the serial interface mode is used, the remaining unused pins on this port can be allocated as General Purpose Input/Output (GPIO).

#### 1.2.6 General Purpose Host Interface Port

The General Purpose Host interface allows connection of moderate-to-relatively slow-speed, third party peripherals such as infrared remote control processors, codec host ports, smart card controllers (etc.). This port allows simultaneous connection to two peripherals gluelessly, or to as many as four peripherals with the use of external glue logic to provide the additional chip selects. This interface can have one upstream and one downstream DMA channel active to or from the external peripherals at any given time. Data bursting is not supported.

CX25800 Data Sheet Product Overview

#### 1.2.7 GPIO Port

The CX25800 provides up to 24 GPIO pins. These GPIO pins are shared with the following pins/ports groups so that the user can determine exactly which pins can be dedicated to specific functions versus general purpose I/O functions.

- MPEG Parallel Data Port

- 2. ITU-R 656 4:2:2 Data Output

- 3. ITU-R 656 4:2:2 Data Input

- 4. Extended VIP Host Port

- 5. Extended General Purpose Host Port (GPHP)

### 1.2.8 Serial Bus Interface

The CX25800's serial bus interface supports both 99.2-kHz timing transactions and 396.8-kHz, repeated start, multibyte sequential transactions. As a serial bus master, the CX25800 can program other devices on the video card, such as MUXs, as long as the device address is known. The CX25800 supports multibyte sequential reads (more than one transaction) and multibyte write transactions (greater than three transactions), which enable communication to devices that support auto-incremental internal addressing.

### 1.2.9 PCI Bus Interface

The CX25800 is designed to efficiently utilize the available 132 MBps PCI bus. The 32-bit dwords are output on the PCI bus with the appropriate image data under the control of the DMA channels. The video stream consumes bus bandwidth with average data rates varying from 44 MBps for full-size 768 576 PAL RGB32, to 4.6 MBps for NTSC CIF 320 240 RGB16, to 0.14 MBps for NTSC ICON 80 60 8-bit mode.

The pixel instruction stream for the DMA channels consumes a minimum of 0.1 MBps. The CX25800 provides the means for mitigating bandwidth bottlenecks caused by slow targets and long bus access latencies that can occur in some system configurations. To overcome these system bottlenecks, the CX25800 gracefully degrades and recovers from FIFO overruns to the nearest pixel in real time.

Product Overview CX25800 Data Sheet

### 1.3 Pin Descriptions

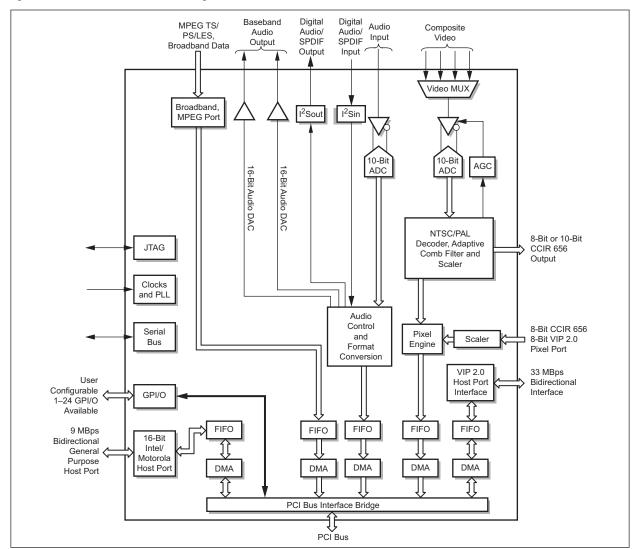

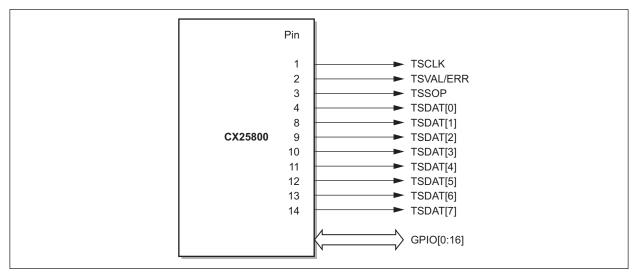

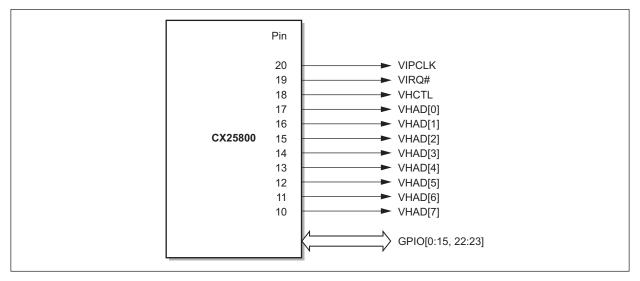

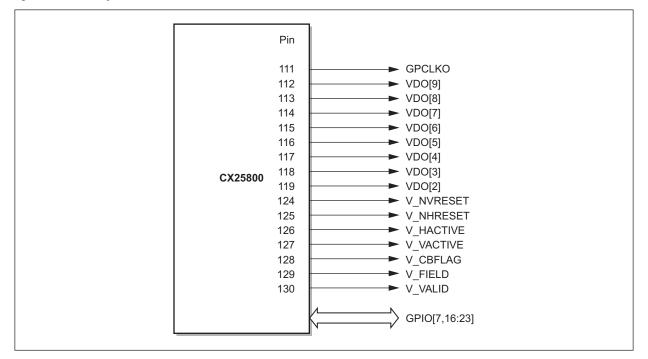

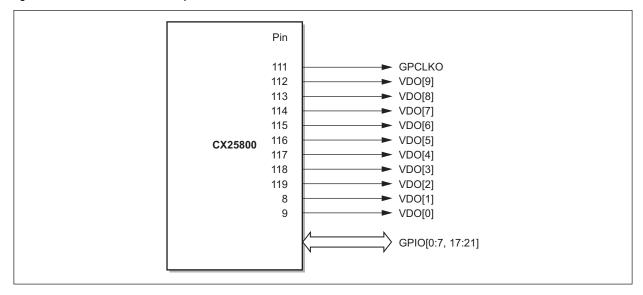

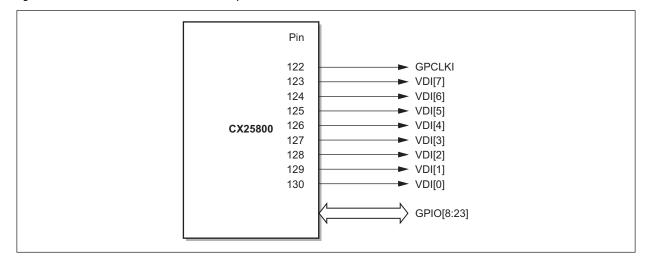

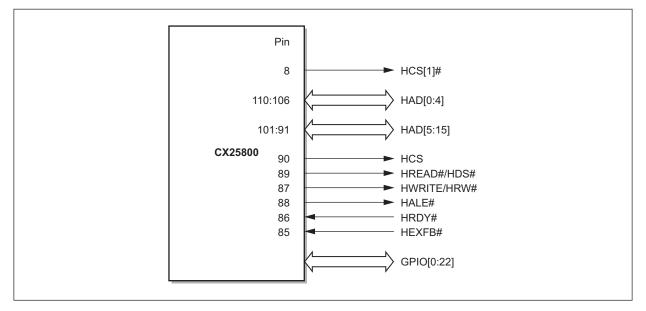

Figure 2 displays the CX25800 pinout diagram. Table 1 provides a description of pin functions grouped by common function.

Figure 2. CX25800 Pinout Diagram

CX25800 Data Sheet Product Overview

Table 1. Pin Descriptions Grouped by Pin Function (1 of 6)

| Pin Number                                        | Pin Name  | Dir | Туре        | Signal                          | Description                                                                                          |

|---------------------------------------------------|-----------|-----|-------------|---------------------------------|------------------------------------------------------------------------------------------------------|

|                                                   |           |     | PCI Interfa | ce (50 Pins)                    |                                                                                                      |

| 63                                                | CLK       | I   | _           | Clock                           | All PCI signals except RST# and INTA# are sampled on the rising edge of this 33.3333 MHz clock.      |

| 22                                                | RST#      | I   | _           | Reset                           | Bus reset causes all PCI outputs to asynchronously three-state.                                      |

| 23                                                | REQ#      | 0   | t/s         | Request                         | Agent requests bus.                                                                                  |

| 24                                                | GNT#      | I   | _           | Grant                           | Agent grants bus.                                                                                    |

| 37                                                | IDSEL     | I   | _           | Initialization Device<br>Select | Selects device during configuration read and write transactions.                                     |

| [28–35, 38–43,<br>48, 49, 60–62,<br>68–72, 74–81] | AD[31:0]  | I/O | t/s         | Address/Data                    | Address phase when FRAME# is 1st asserted, and data transfer when IRDY# and TRDY# are both asserted. |

| [36, 50, 59, 73]                                  | CBE[3:0]# | I/O | t/s         | Bus Command/<br>Byte Enables    | Bus transaction-type command during address phase, and byte enables during entire data phase.        |

| 58                                                | PAR       | I/O | t/s         | Parity                          | Even parity across {AD, C/BE#}, lags address/data phase                                              |

| 51                                                | FRAME#    | I/O | s/t/s       | Cycle Frame                     | Asserted to begin bus transaction. Deasserted when transaction in final data phase.                  |

| 52                                                | IRDY#     | I/O | s/t/s       | Initiator Ready                 | Indicates the initiator is ready to accept read data or has placed valid write data on the AD.       |

| 53                                                | TRDY#     | I/O | s/t/s       | Target Ready                    | Indicates the target is ready to accept write data or has presented valid data on AD during a read.  |

| 54                                                | DEVSEL#   | I/O | s/t/s       | Device Select                   | Indicates the driving device has decoded the address as the target of the current access.            |

| 55                                                | STOP#     | I/O | s/t/s       | Stop                            | Target requesting master to stop current transaction.                                                |

| 56                                                | PERR#     | I/O | s/t/s       | Parity Error                    | Report data parity error.                                                                            |

| 57                                                | SERR#     | 0   | t/s         | System Error                    | Report address parity or system error.                                                               |

| 21                                                | INTA#     | 0   | t/s         | Interrupt A                     | Request an interrupt.                                                                                |

|                                                   | •         | •   | JTAG Sign   | als (4 Pins)                    |                                                                                                      |

Product Overview CX25800 Data Sheet

Table 1. Pin Descriptions Grouped by Pin Function (2 of 6)

| Pin Number            | Pin Name                                | Dir     | Туре             | Signal                               | Description                                                                                                                                                      |

|-----------------------|-----------------------------------------|---------|------------------|--------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 169                   | TCK                                     | I       | _                | Test Clock                           | Used to synchronize all JTAG test structures. Tie low when not using JTAG.                                                                                       |

| 168                   | TMS                                     | I       | r                | Test Mode Select                     | Transitions drive JTAG state machine sequence. Tie high or leave floating when not using JTAG. A fixed sequence on this pin initializes the JTAG tap controller. |

| 167                   | TDI                                     | I       | r                | Test Data In                         | Load input instructions and/or test vector data for boundary scan and internal scan. Tie high or leave floating when not using JTAG.                             |

| 158                   | IREFX—TDO                               | 0       |                  | Test Data Out                        | Output for verifying JTAG serial operations. The output is three-stated when not using JTAG port.                                                                |

|                       |                                         | VIP 2.0 | O Host Master Si | gnals (5 or 11 Pins)                 |                                                                                                                                                                  |

| 16, 17<br>8–15        | VHAD[1:0] <sup>(1)</sup><br>GPIO[23:16] | I/O     | _                | VIP Host Address/<br>Data            | VIP Address and Data bus, defaults to VIP1.1 interface with 2 addr/data pins. Can be configured as VIP 2.0 with 8 address/ data pins (GPIO).                     |

| 18                    | VHCTL                                   | I/O     | _                | VIP Host Control                     | VIP System Host control                                                                                                                                          |

| 19                    | VIRQ#                                   | I/O     | od               | VIP Interrupt<br>Request             | VIP Interrupt Request (open drain)                                                                                                                               |

| 20                    | VIPCLK                                  | 0       | _                | VIP Clock                            | VIP master output clock. This clock is buffered. PCI CLK = 33.3333 MHz.                                                                                          |

|                       |                                         | Trans   | sport Stream Sig | nals (4 or 11 Pins)                  |                                                                                                                                                                  |

| 4                     | TSDAT[0] <sup>(2)</sup>                 | I       | _                | Transport Stream<br>Data             | Transport Stream Input data bus. TSDAT[0] is used in serial mode.                                                                                                |

| 3                     | TSSOP                                   | I       | _                | Transport Stream<br>Start of Packet  | Transport Stream Start-of-Packet indicator.<br>Indicates first byte in serial or parallel<br>transport packet.                                                   |

| 2                     | TSVAL/ERR                               | I       | _                | Transport Stream<br>Error/Valid      | Transport Stream Error or Valid indicator                                                                                                                        |

| 1                     | TSCLK                                   | I       | _                | Transport Stream<br>Clock            | Transport Stream input clock. All other transport stream inputs are sampled on the rising (falling) edge of TSCLK.                                               |

|                       | •                                       |         | Host Master Sig  | nals (22 Pins)                       | ,                                                                                                                                                                |

| [91–101, 106–<br>110] | HAD[15:0]                               | 1/0     | _                | General Purpose<br>Host Address/Data | Bidirectional address/data access bus                                                                                                                            |

| 90                    | HCS#                                    | 0       | _                | General Purpose<br>Host Chip Select  | External chip select                                                                                                                                             |

CX25800 Data Sheet **Product Overview**

Table 1. Pin Descriptions Grouped by Pin Function (3 of 6)

| Pin Number                  | Pin Name      | Dir | Туре             | Signal                                           | Description                                                                                                                                    |

|-----------------------------|---------------|-----|------------------|--------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------|

| 89                          | HRD#/<br>HDS# | 0   | _                | General Purpose<br>Host Read/Data<br>Strobe      | Either the active-low read signal or the programmable polarity data strobe signal                                                              |

| 88                          | HALE#         | 0   | _                | General Purpose<br>Host Address Latch<br>Enable  | Address Latch Enable signal, used only in multiplexed 16-bit address/data mode                                                                 |

| 87                          | HWR/<br>HRW#  | 0   | _                | General Purpose<br>Host Write/Read,<br>not Write | Either the active-low write signal or the read/write bar                                                                                       |

| 86                          | HRDY#         | I   | r                | General Purpose<br>Host Ready                    | External data transfer acknowledge signal                                                                                                      |

| 85                          | HEXFB         | I   | r                | General Purpose<br>Host External<br>Status       | Handshaking signal for use in DMA mode to indicate the status of the external source or destination FIFO.                                      |

|                             | 1             | G   | PIO/Serial Bus/I | Reset (29 Pins)                                  |                                                                                                                                                |

| [8–15, 112–119,<br>123–130] | GPIO[23:0]    | I/O | I/O              | GPIO                                             | See GPIO Cross-Reference Table.                                                                                                                |

| 122                         | GPCLKI        | I   | I                | General Purpose<br>Input Clock                   | Digital Video Input Reference clock                                                                                                            |

| 111                         | GPCLKO        | 0   | 0                | General Purpose<br>Output Clock                  | Digital Video Output Reference clock                                                                                                           |

| 132                         | SID           | I/O | od               | Serial Data                                      | Bit data or acknowledge                                                                                                                        |

| 131                         | SIC           | I/O | od               | Serial Clock                                     | Bit clock                                                                                                                                      |

| 170                         | SYS_RSTO#     | 0   | t/s              | System Reset Out                                 | Logical PCI reset, soft reset, or power-on reset output. This is used to reset CX25800's peripheral under software control or with hard reset. |

|                             |               |     | Digital Audi     | o (6 Pins)                                       |                                                                                                                                                |

| 171                         | ADATI         | 1   | r                | Audio Data In                                    | Bit Serial Input data                                                                                                                          |

| 172                         | ALRCKI        | 1   | r                | Audio Left/Right<br>Clock In                     | Left/Right Framing Input clock                                                                                                                 |

| 173                         | ASCKI         | I   | r                | Audio Serial Clock<br>Input                      | Bit Serial Input clock                                                                                                                         |

| 174                         | ADATO         | 0   | r                | Audio Data Out                                   | Bit Serial Output data                                                                                                                         |

| 175                         | ALRCKO        | 0   | r                | Audio Left/Right<br>Clock Out                    | Left/Right Framing Output clock                                                                                                                |

CX25800 Data Sheet **Product Overview**

Table 1. Pin Descriptions Grouped by Pin Function (4 of 6)

| Pin Number | Pin Name         | Dir | Туре               | Signal                       | Description                                                                                                                                                      |

|------------|------------------|-----|--------------------|------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 176        | ASCKO            | 0   | r                  | Audio Serial Clock<br>Output | Bit Serial Output clock                                                                                                                                          |

|            |                  | С   | rystal Interface S | Signals (4 Pins)             |                                                                                                                                                                  |

| 134        | XT2              | 0   | _                  | XT2                          | Crystal oscillator pin                                                                                                                                           |

| 135        | XT1              | I   | _                  | XT1                          | Crystal oscillator or clock oscillator input pin can be connected to XT1.                                                                                        |

| 133        | VAXTL            | _   | _                  | PSUP_XTAL                    | XTAL and Sample and Hold digital power/                                                                                                                          |

| 136        | AGXTL            | _   | _                  | NSPU_XTAL                    | ground. Nominal VA = 3.3 V.                                                                                                                                      |

|            |                  |     | ADC Interfac       | e (23 Pins)                  |                                                                                                                                                                  |

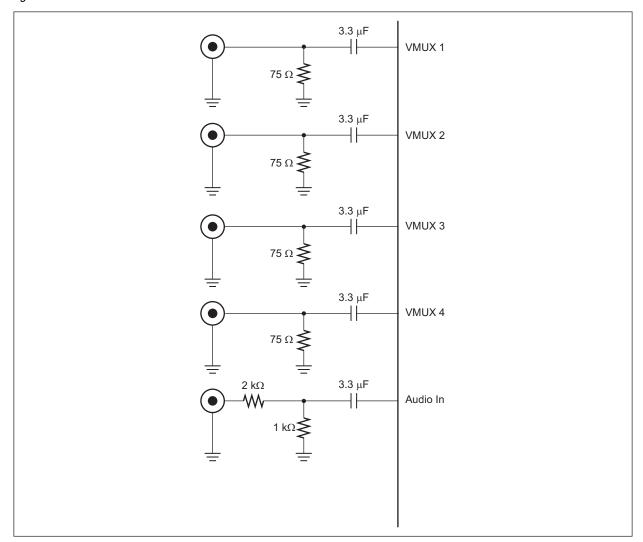

| [145:142]  | VMUX[1:4]        | I   | А                  | Video Mux {1:4}              | Analog composite video inputs to the on-<br>chip 4:1 analog multiplexer. Leave unused<br>inputs No Connect. Grounding unused<br>inputs may draw excessive power. |

| 150        | Reserved         |     |                    |                              | Leave this pin No Connect                                                                                                                                        |

| 151        | AUDIO IN         | 1   | А                  | Audio IN                     | Analog audio input. Leave unused input No Connect or connected to ground via a decoupling capacitor. Grounding this input may draw excessive power.              |

| 138<br>156 | VCM1<br>VCM2     | 0   | А                  | VCM_ADC{1:2}                 | Common mode voltage reference                                                                                                                                    |

| 140<br>154 | VREFN1<br>VREFN2 | 0   | А                  | VREFN{1:2}                   | Input Negative reference (1.0 V)—one for each Y and C/Aud ADCs, cap to AGA.                                                                                      |

| 139<br>155 | VREFP1<br>VREFP2 | 0   | А                  | VREFP{1:2}                   | Input Positive reference (1.8 V)—one for each Y and C/Aud ADCs, cap to AGA.                                                                                      |

| 153        | VBGOUT           | 0   | А                  | VBGOUT                       | Voltage reference 1.21 V nominal, cap to AGA.                                                                                                                    |

| 137, 157   | VAA{1:2}CR       | _   | Α                  | VAA{1:2}CR                   | A/D core power/ground. Nominal                                                                                                                                   |

| 141, 152   | AGA{1:2}CR       | _   | А                  | AGA{1:2}CR                   | VA = 3.3 V                                                                                                                                                       |

| 146        | ASUB             | _   | _                  | ASUB                         | A/D core substrate (ground)                                                                                                                                      |

| 147        | VAASH            | _   | _                  | PSUPA_SHA_ADC                | A/D Sample and Hold Analog power/                                                                                                                                |

| 148        | AGASH            | _   | _                  | NSUPA_SHA_ADC                | ground. Nominal VA = 3.3 V.                                                                                                                                      |

CX25800 Data Sheet **Product Overview**

Pin Descriptions Grouped by Pin Function (5 of 6) Table 1.

| Pin Number                     | Pin Name  | Dir    | Туре            | Signal              | Description                                                                                                                                |

|--------------------------------|-----------|--------|-----------------|---------------------|--------------------------------------------------------------------------------------------------------------------------------------------|

| 149                            | VGND      | I      | A/D             | Virtual Ground      | Single-end-to-differential converter input for common-mode noise rejection. Connect to analog ground through 3.3 $\mu F$ series capacitor. |

| 105, 165                       | VPP1/VPP2 | _      | _               | VPP1, VPP2          | PLL power supply. VD = 1.8 V.                                                                                                              |

| 104, 166                       | PGND      | _      | _               | PGND                | PLL return supply                                                                                                                          |

| 158                            | IREFX_TDO | I/O    | A/D             | IREF_EXT/TDO        | Shared analog current ref pin JTAG TDO pin                                                                                                 |

|                                |           | Au     | dio Output DAC  | Signals (6 Pins)    |                                                                                                                                            |

| 159                            | VADA      | _      | _               | VADA                | DAC analog core power and ground.<br>VA = 3.3 V                                                                                            |

| 164                            | AGDA      | _      | _               | AGDA                | VA = 3.3 V                                                                                                                                 |

| 163                            | LASCO     | 0      | А               | LASCO               | DAC Pulse Width Modulator (PWM), left stereo audio output channel                                                                          |

| 160                            | RASCO     | 0      | А               | RASCO               | DAC PWM, right stereo audio output channel                                                                                                 |

| 161                            | PWM_REF2  | 0      | A               | PWM_REF2            | Audio DAC reference, right                                                                                                                 |

| 162                            | PWM_REF1  | 0      | А               | PWM_REF1            | Audio DAC reference, left                                                                                                                  |

|                                | 1         | I/O an | d Core Power ar | nd Ground (23 Pins) |                                                                                                                                            |

| 6, 26, 45, 65, 83,<br>103      | VDD       | _      | _               | VDD                 | Digital core power supply. Nominal VDD = 1.8 V.                                                                                            |

| 7, 27, 44, 64, 82,<br>120      | GND       | _      | _               | GND                 | Ground for digital core (GND)                                                                                                              |

| 5, 25, 46, 66, 84,<br>102, 121 | VDDIO     | _      | _               | VDDI and VDDO       | Digital inputs/outputs power supply. VD = 3.3 V.                                                                                           |

| 47, 67                         | VIO       | _      | _               | VIO                 | +5 V reference for 5 V-tolerant PCI input buffers                                                                                          |

Product Overview CX25800 Data Sheet

#### Table 1. Pin Descriptions Grouped by Pin Function (6 of 6)

| Pin Number | Pin Name | Dir | Туре | Signal | Description |

|------------|----------|-----|------|--------|-------------|

|------------|----------|-----|------|--------|-------------|

#### **FOOTNOTES:**

(1) VHAD[1:0] is the default for the 5-pin VIP Host Port setting.

(2) TSDAT[0] is the default for the 4-pin serial MPEG Data Port setting. The 11-pin setting shares GPIO pins.

#### **GENERAL NOTES:**

1. Type:ractive resistive pull-up

od: open-drain

t/s: three-state

s/t/s: sustained three-state

[x:y]: Bus

{u:v:}Array of signal ports—expand to number without braces.

- 2. All signal I/O are LVTTL compatible (3.3 V operation with 3.9 V tolerance), except for the PCI signals which are all 5.5 V tolerant.

- 3. All inputs are Schmitt unless otherwise noted. The PCI inputs do not have hysteresis.

- 4. All outputs have drive capability  $I_{OL} = 4$  mA unless otherwise noted.

## **Functional Description**

### 2.1 Audio Input

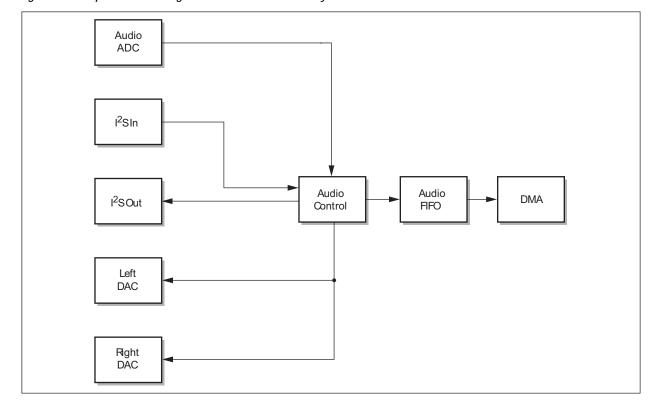

This section describes the functionality of the analog audio input. The following paragraphs define the logical sequence, from the audio input at the analog front end, to the output of digital audio samples, to the PCI bus or on-board DACs.

#### 2.1.1 Overview

Analog audio input can be output directly to the on-board DACs for connection to the PC's sound card, to I<sup>2</sup>S for high-fidelity digital coaxial and optical interfaces, or to the host for software-based playback or encoding.

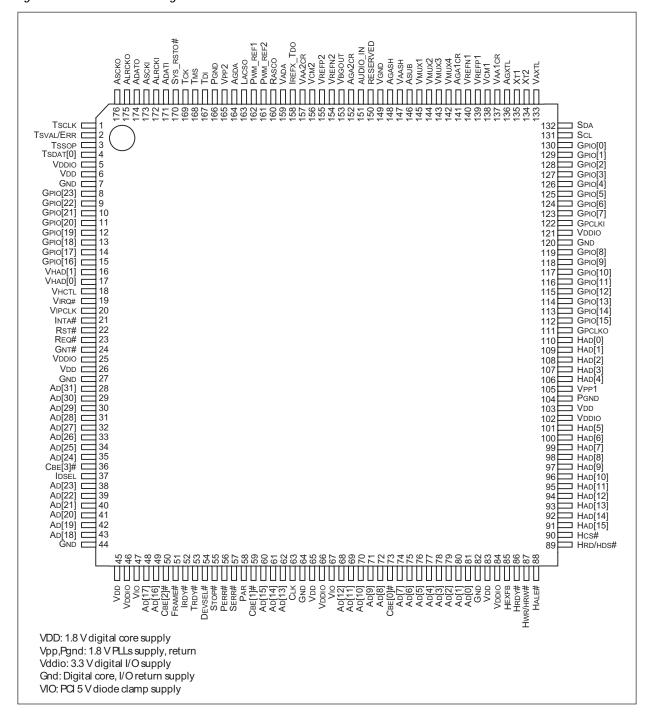

The major functional blocks of the audio subsystem are illustrated in Simplified Block Diagram of CX25800 Audio Subsystem and are broken down into the following sections:

- ◆ Audio-ADC

- · Audio PLL initialization

- Input source select

- Dematrix control

- Audio control and Sample Rate Converter

- I<sup>2</sup>S input and output

- Audio DACs

Functional Description CX25800 Data Sheet

Figure 3. Simplified Block Diagram of CX25800 Audio Subsystem

### 2.1.2 Analog Input ADC

The CX2500's Audio input (pin 151) is used for sampling line level audio signals from an amplified microphone.

#### 2.1.3 Audio PLL Initialization

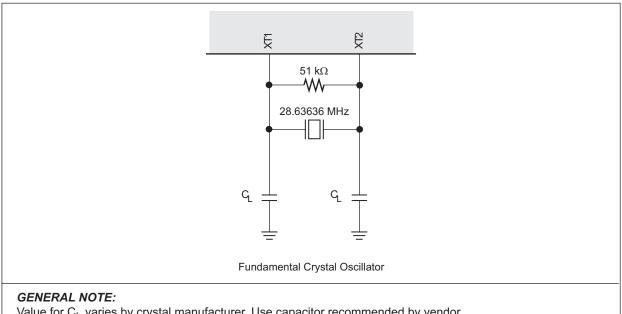

The audio PLL is automatically configured for 28.636363-MHz crystal frequency with the AUD\_INIT\_LD register. If using a crystal of frequency other than 28.636363 MHz, please contact Conexant Applications Engineering. If using the I<sup>2</sup>S output mode, the PLL must be programmed to exactly 221.184 MHz in fractional mode.

CX25800 Data Sheet Functional Description

### 2.1.4 Input Source Select

The 12 LSBs [11:0] of the AUD\_CTL register (location 24'h32058C) determine the desired operation of the audio decoder.

### 24'h32058C—AUD\_CTL Register

| Bits  | Type | Default  | Name                       | Description                                       |

|-------|------|----------|----------------------------|---------------------------------------------------|

| [5:0] | RW   | 6'h00    | Reserved                   | Reserved                                          |

| [6]   | RW   | 1'b0     | Reserved                   | Reserved                                          |

| [8:7] | RW   | 2'h0     | Reserved                   | Reserved                                          |

| [9]   | RW   | Reserved | Reserved                   | Reserved                                          |

| [10]  | RW   | 1'b0     | Reserved                   | Reserved                                          |

| [11]  | RW   | 1'b0     | Reserved                   | Reserved                                          |

| [12]  | RW   | 1'b0     | DAC_ENABLE                 | DAC enable bit                                    |

| [13]  | RW   | 1'b0     | I <sup>2</sup> SOUT_ENABLE | I <sup>2</sup> S output enable bit                |

| [14]  | RW   | 1'b0     | I <sup>2</sup> S_STR2DAC   | I <sup>2</sup> S input straight to DAC enable bit |

| [15]  | RW   | 1'b0     | I <sup>2</sup> SIN_ENABLE  | I <sup>2</sup> S input enable bit                 |

### 2.1.5 Audio Control and Sample Rate Converter

#### 2.1.5.1 Audio Demodulator Sample Rate Converter

Audio formats supported by the CX25800 are upconverted from their native sampled format to 48 kHz. This simplifies internal filtering and interfacing to external hardware peripherals through  $\rm I^2S$ , the internal audio DACs, or to software codecs.

#### 2.1.5.2 Volume

The volume control provides gain to both the left and right audio channel in 1 dB increments. The volume range is –63 to 0 dB and is controlled by the VOL\_CTL register.

In addition, flexible control over muting is possible by the ability to control the muting of the selected source from the audio demodulator, the I<sup>2</sup>S output, and the audio DAC. During initialization, from reset to the end of the AUD\_START\_TIMER count, all three of these mutes are enabled automatically to avoid pops or clicks on any of the outputs.

Functional Description CX25800 Data Sheet

### 24'h320594—VOL\_CTL Register

| Bits   | Туре | Default | Name                     | Description                             |

|--------|------|---------|--------------------------|-----------------------------------------|

| [5:0]  | RW   | 8'h00   | VOLUME                   | Volume control in dB steps, 0 to -63 dB |

| [6]    | RW   | 1'b0    | SRC_MUTE_EN              | Source mute enable                      |

| [7]    | RW   | 1'b0    | I <sup>2</sup> S_MUTE_EN | I <sup>2</sup> S mute enable            |

| [8]    | RW   | 1'b0    | DAC_MUTE_EN              | DAC mute enable                         |

| [15:9] | RW   | 7'h00   | _                        | Reserved                                |

#### 2.1.5.3 Balance

The DAC output level can be adjusted. Digital balance control is used to alter the relative gain between the left and right channel outputs. Balance is controlled by providing an attenuation to one channel while maintaining 0 dB gain to the other channel. Attenuation of either channel is in the range of -63 to 0 dB in 1 dB steps. Balance attenuation is performed prior to the volume control. Stereo is only available via I<sup>2</sup>S input. The analog audio input is monophonic.

### 24'h320598—BAL\_CTL Register

| Bits   | Туре | Default | Name      | Description                                                                                 |

|--------|------|---------|-----------|---------------------------------------------------------------------------------------------|

| [5:0]  | RW   | 8'h00   |           | Attenuation to be provided to the selected channel in dB. Range is 0 to $-63~\mathrm{dB}$ . |